计组实验-存储器

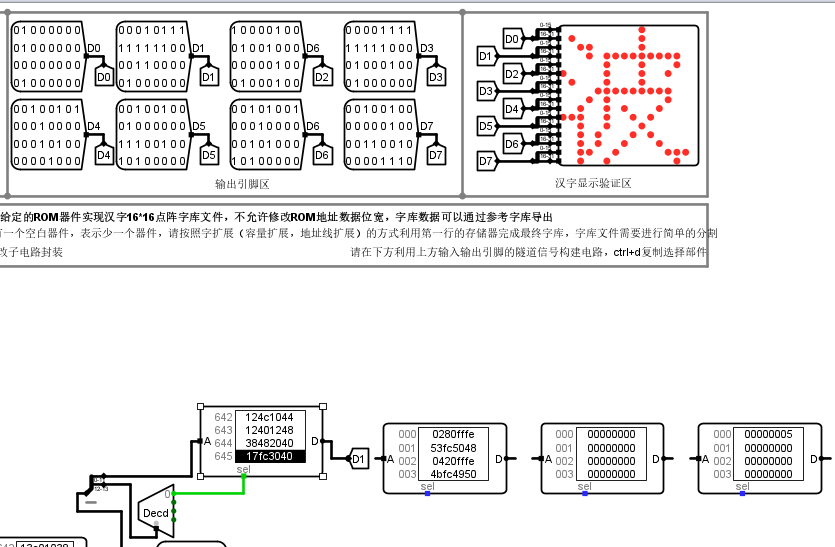

拓展字

将一片14位的ROM改为用4片12位的ROM完成

片选信号sel的加入

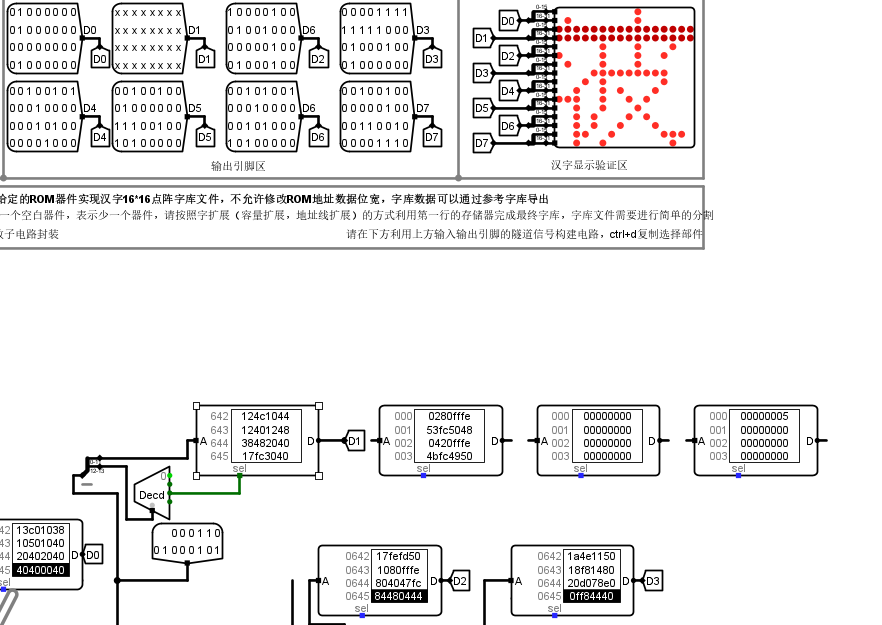

整体连接

测试结果

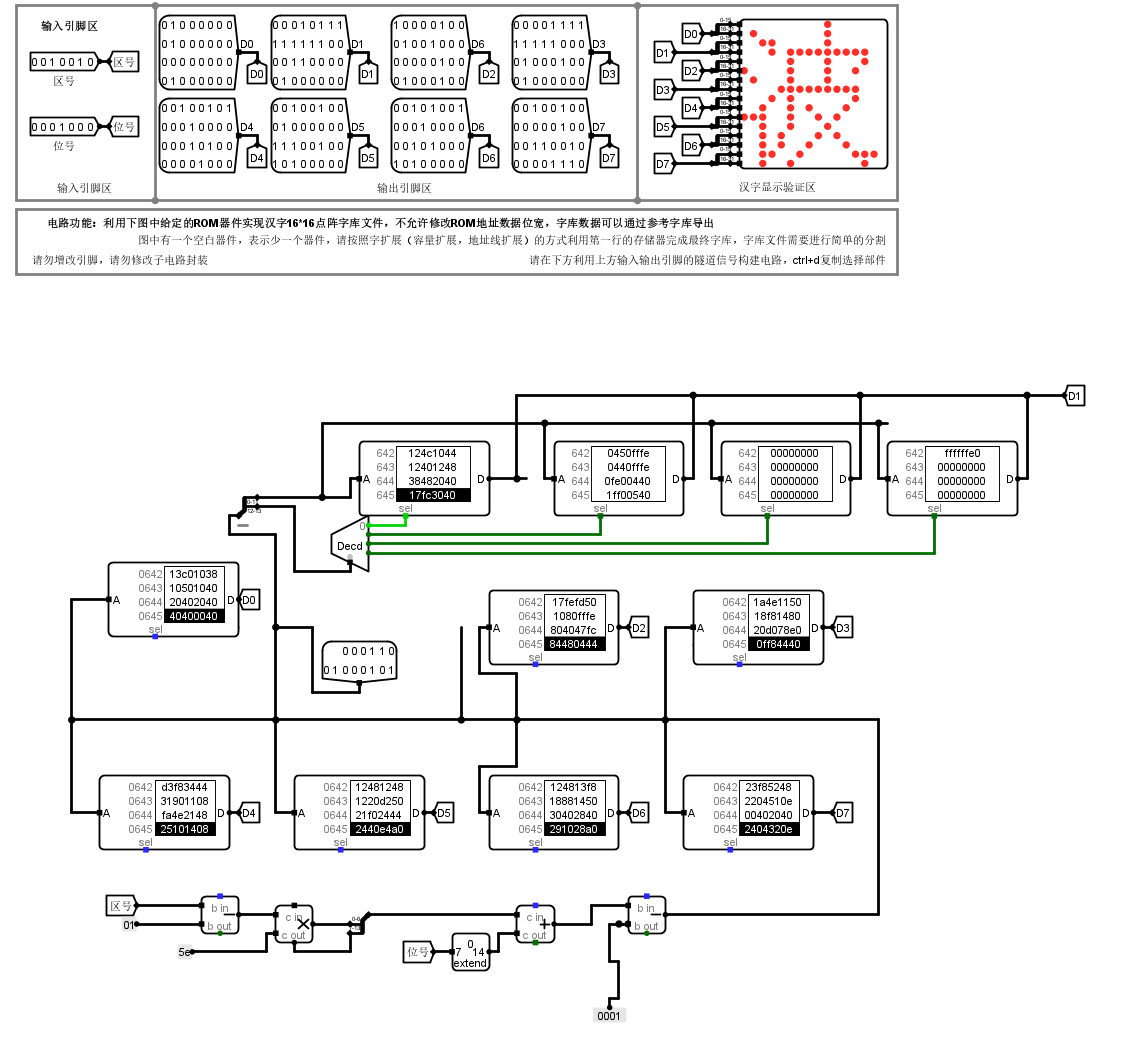

MIPS-RAM访问方式控制

调试

前后历经长时间调试,总结核心如下:

3种形式下的访问方式的地址判断

00:字,末两位无效-》4片RAM全部输出(4个字节)

01:字节,皆有效-》唯一有效的1片RAM输出(1个字节)

10:双字节,末一位无效-》有效的2片RAM输出(2个字节)

输入格式和输出格式(※重点注意)

都将有效数据放置在最低位,则输入和输出需要根据不同的访问方式进行格式转换,本次实现分别通过两种方式,分别是:

输入:移位

输出:数据选择

详细步骤

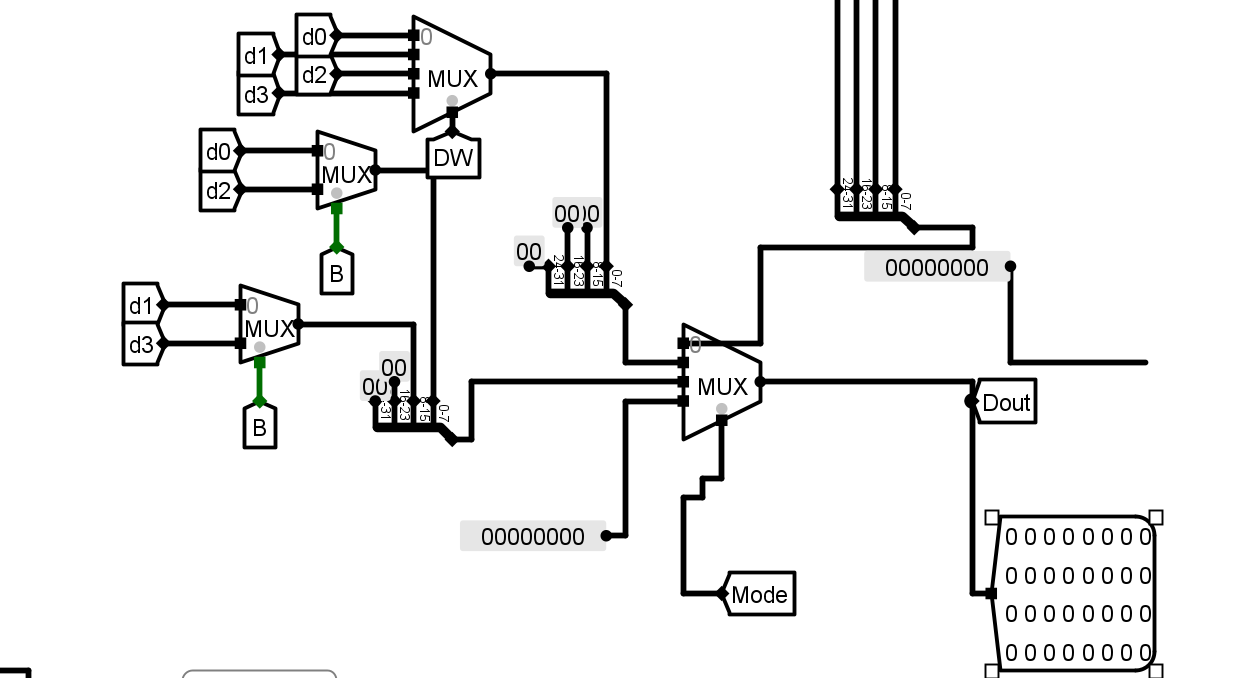

输入格式

把输入数据进行移位,采取方式,循环移位

如果访问方式为01——按字节访问,对3种不同的进行移位:

同理,对于10模式

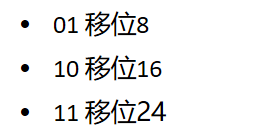

输出格式

根据3种访问方式,由数据选择器完成结果的呈现,其中:

DW是单字节访问的末两位

B是双字节访问的有效位(倒数第2位)

d3\d2\d1\d0分别为从高到低RAM的输出数据

片选信号

在高字节读写时,发生如下错误

说明写入时覆盖了本不需要写入的值,因此根据此前的设计添加片选信号。分别将各片ram有效的情况通过或门写出,以是完成片选信号的产生。

最终结果

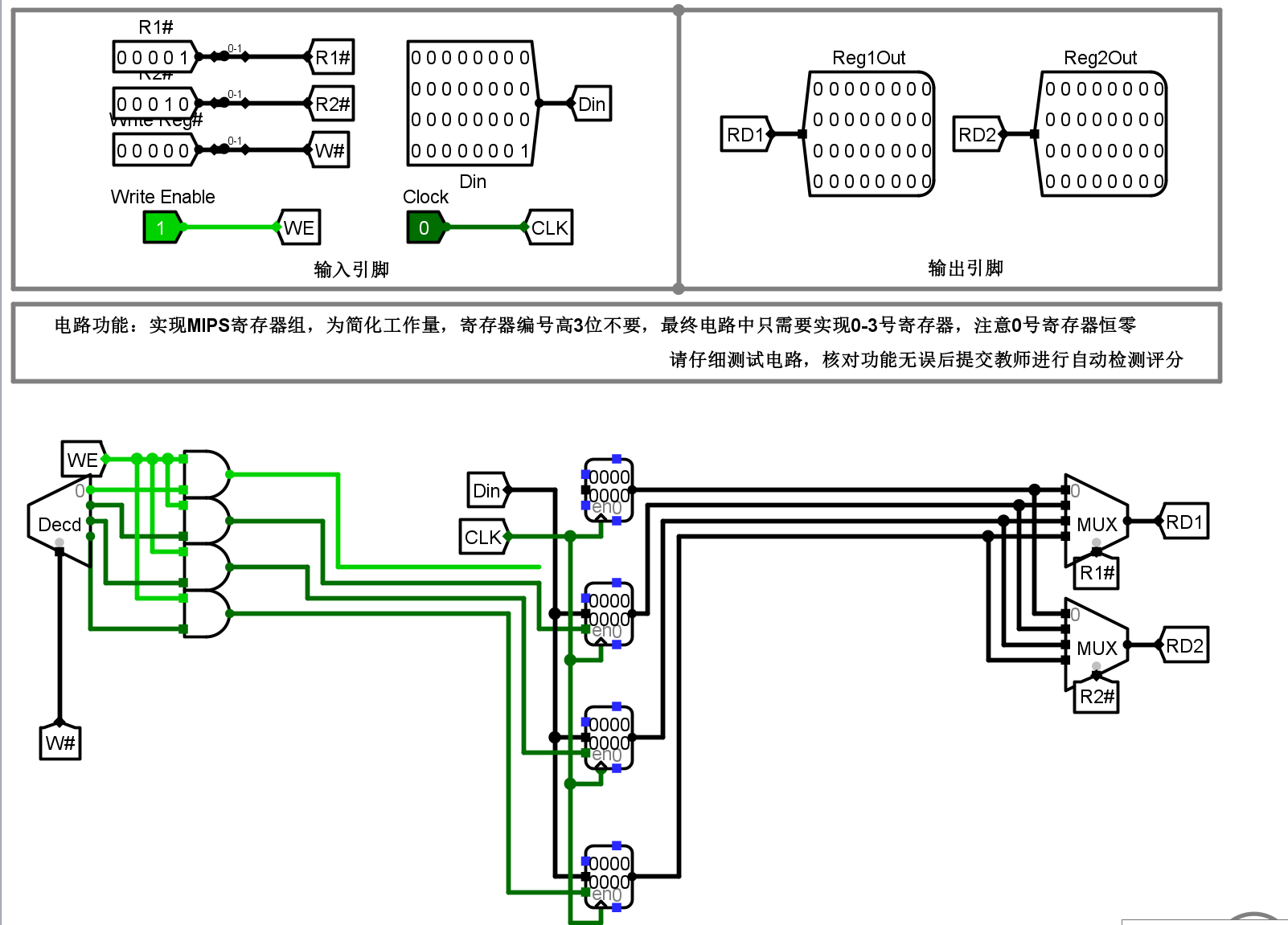

MIPS-Regfile

需要注意的问题是一点,需要注意0号寄存器恒零

则不对0号寄存器进行写入操作即可

电路连接

测试结果

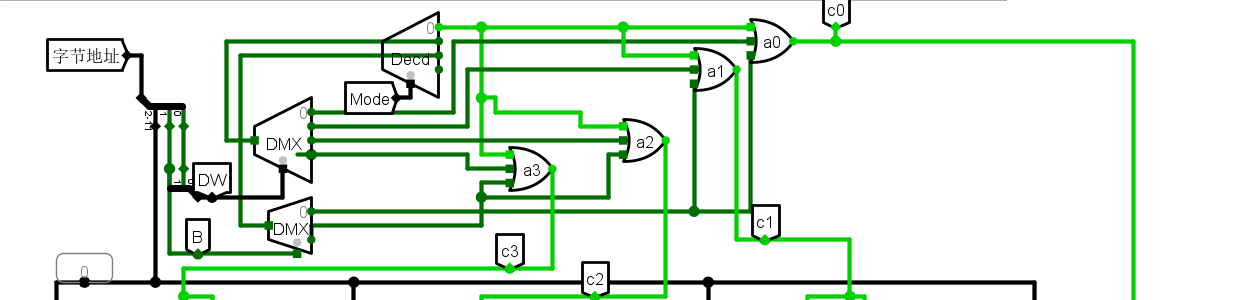

cache直接相联

将cache的工作原理进行了解,并学习了不同的地址映射方式——主存地址向cache行的映射。这里运用直接相联映射方式进行实现

思路与实现

如果是直接相联区分一个cache块中有多少大小的字节

cache大小目前自己定,则8行*1块(4个字节)

判断地址,当地址能在相应行时,再判定tag是否一致

将2-4与位置进行比较,故需要用译码器,输出cache中的tag

若tag不一致,进行置换,两部分:数据块与tag

条件:既片选,又miss

Tag条件,如果有效,再进行判定

输出结果,根据数据块中block offset导出数据结果

有效位valid如果没有内容,置0,若有,置1