Verilog Ethernet与加热电压闭环实验

1. Verilog Ethernet

Github上给出的开源以太网构建方案Verilog Ethernet,可用于构建1G,10G,25G以太网,可以基于Xilinx或Intel FPGA构建,包括 Kintex7 XC7K325T和Artix7 XC7A35T。

暂时还没有找到直接描述该项目的论文,作者的另一个项目里面使用了该项目里面的代码。知乎作者王小二苕给出了他在EP4CE10平台上移植该工程的过程,结果是可以实现板卡与上位机通过UDP通信。

2. 电源控制闭环

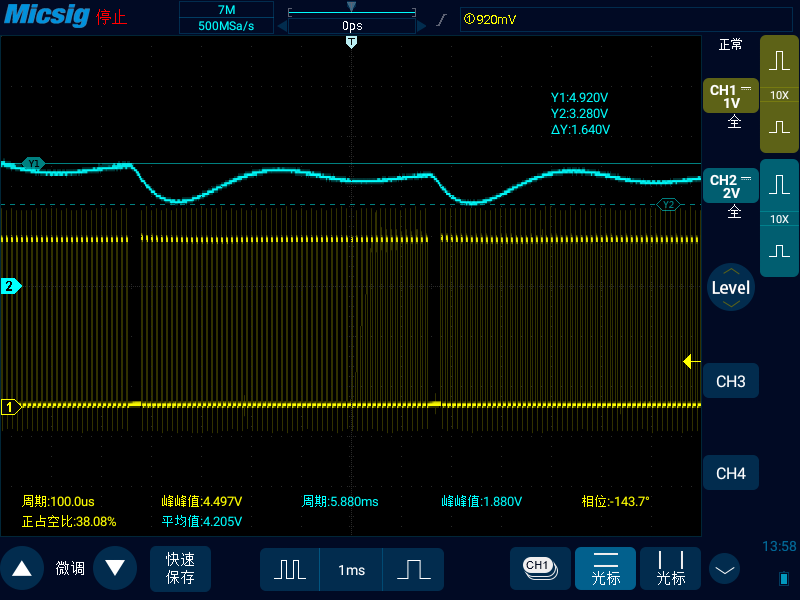

加热电压单闭环实验于佛祖岭FRC装置现场进行。第一次调试发现加热输出电压波动很大,PWM输出信号缺了一个周期的脉冲,最终可以保持加热电压稳定。实验室复现该现象,结果如下。大概是6ms缺失一次脉冲。

该现象在对控制板进行复位后,第一次设定加热PWM信号占空比,输出的加热PWM波形没有缺失脉冲。第二次对所有通道进行复位后再次设定加热占空比,则出现该现象,说明问题有可能出现在给出的指令上。

清零指令为 #02SET;{0;0,1;0,2:0,3:0,4:0,5:0,6:0,7:0,8:0,9:0,10:0};$,其中1通道直接控制PWM占空比,2-4为PID参数,5通道设定PID工作模式,6通道为PID目标值,7通道为PID反馈值,这里等于PWM占空比测量值,8通道为PID计算输出值,会给到1通道。1通道工作时的设定值来自清零指令和PID计算输出值,应该是这两个指令在某一时刻同时作用于1通道,导致1通道该时刻被清零,导致缺脉冲现象出现。

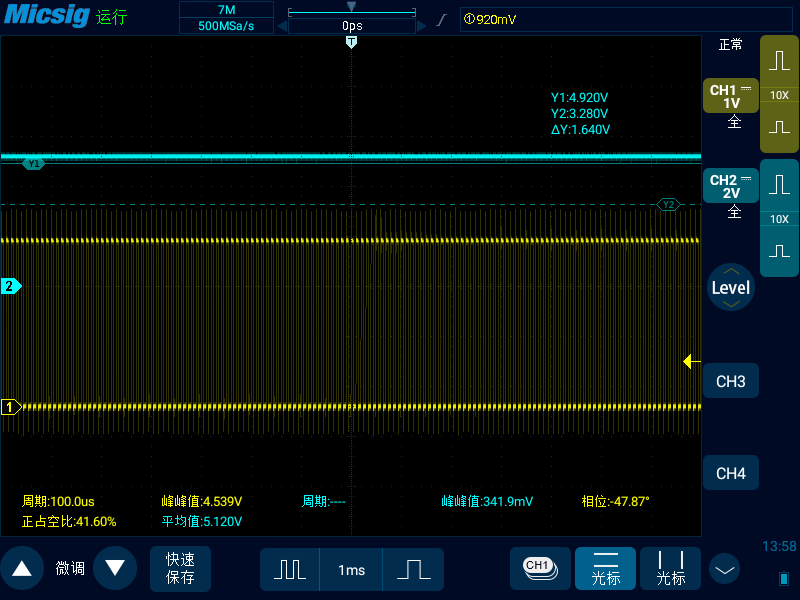

后面修改了清零指令,仅对PID通道进行清零,指令为:#02SET;{2:0,3:0,4:0,5:0,6:0};$,测量波形如下,没有出现缺脉冲现象发生。建议中控初始化加热相关通道时,仅对单次操作的通道进行清零,而工作状态下反复写入的通道则不进行操作,即仅初始化2-6通道,1通道写入值完全由PID输出决定。

3. PicoDAQ

板卡已经全部拿到,初步上电,ESP32核心运行正常。目前还没有相关固件,暂时没有做相关的功能验证。电池和接口已经再采购中,预计下周可以拿到。

接口文档,根据设计图纸初步写了一版描述,已经提供给相关同学参考。

下周计划

- 将

PicoDAQ组装完成,拿到相关固件并进行相关测试。 - 尝试将

Verilog Ethernet工程移植到现有的FPGA板卡上,看能否与上位机通信。 - 加热电压闭环方面,需要测试得到加热电压与程序测量出的PWM占空比的关系,方便后续使用。

本文章使用limfx的vscode插件快速发布