以太网工程生成-定时电路设计

最近工作

-

Verilog Ethernet

-

按照网上给出的简易教程恢复出来了作者给出的例程。

-

作者的例程都是在Linux下编辑的,

Example文件夹下只有一些与开发板相关的源代码和make文件,无法直接导入到vivado中使用。因此先安装了Cygwin和GNU,使电脑能够模拟Linux运行环境。后续更换电脑后由于安装Git,采用自带的Git-Bash结合GNU,运行给出的make文件后生成了系统工程,可以导入到vivado中运行。 -

目前手头只有Artix7型号的板卡,

Example中有两个同型号芯片的工程,分别基于Arty-A7和Nexys-A7,不同在于以太网方案不同。Arty-A7采用DP83438PHY,基于MII的100M以太网。Nexys-A7采用RTL8211E-VBPHY,基于RGMII的1G以太网。

-

手头板卡的以太网方案是

RTL8211FDPHY,基于RGMII的1G以太网。之前用的Arty-A7工程,更改xdc文件时看原理图发现两者方案不同,后面已经更改成Nexys-A7工程。但是不同的时手头板卡的Nexys板卡的PHY接线不同,预计要先更改引脚然后烧录进板卡看一下是否可行。

-

-

电源定时设计

-

电源定时要求定时关机

15min,启动运行5s,其中关机时间由硬件控制,启动时间由软件控制。软件控制由ESP32核心计数控制,与硬件无关;15min定时则与硬件相关,且要求误差不能太大。 -

设计目标:

-

定时关机

15min,误差小于5%,最大不超10%。 -

需要考虑硬件运行环境,主要考虑工作温度,预计

-25°C~85°C运行温度区间。

-

-

原理图设计

-

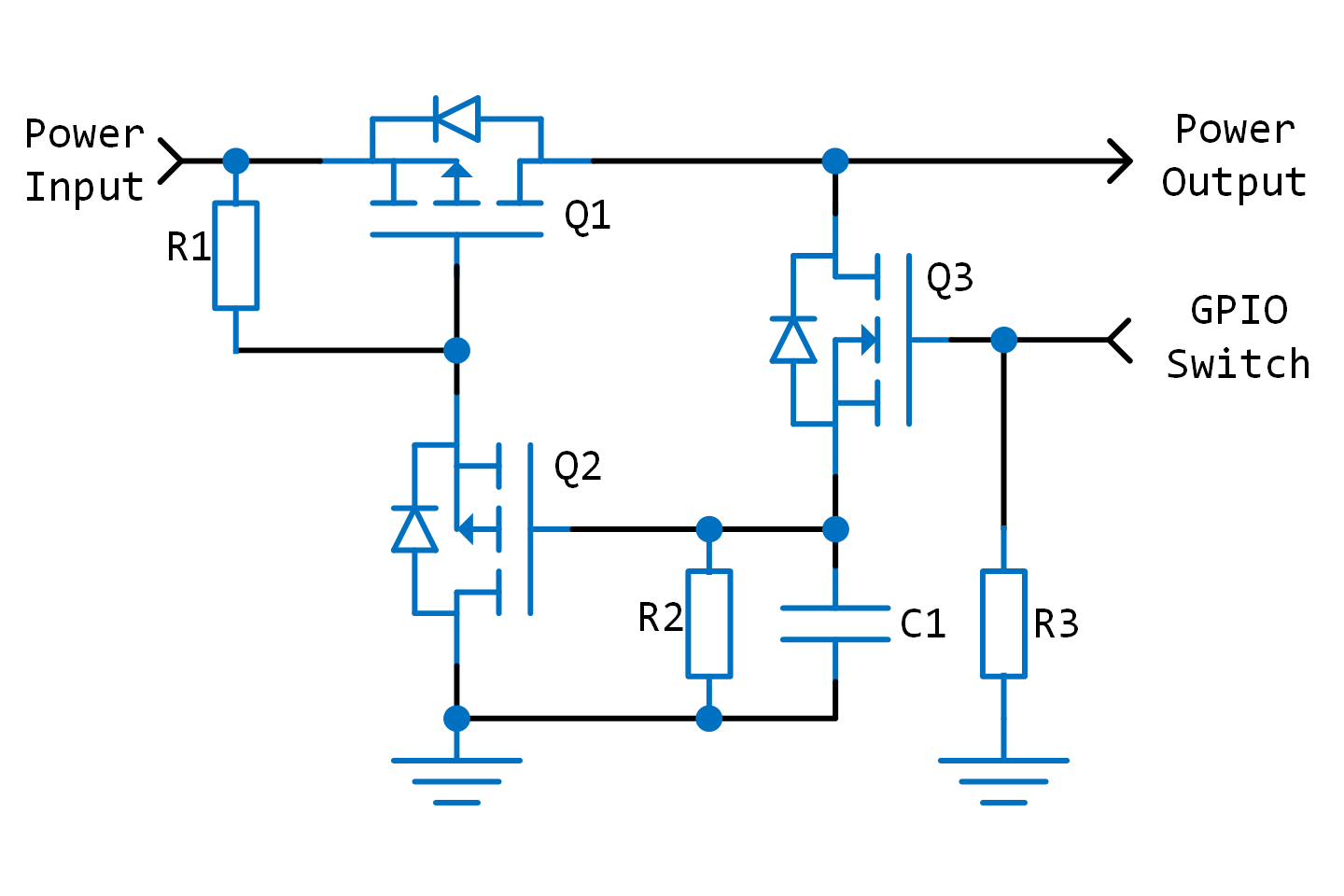

给出原始原理图,如下。主要分别为四个部分,

Q1 PMOS构成的主电源开关,R2-C1构成的定时电路,PMOS Q2构成的主电源开关控制,以及Q3 NMOS构成的充电电路。

-

主要原理为:开始上电时

C1没有电荷,为0V,而Q1 Q2栅极均被R1拉高至电源电压,使得PMOS Q2导通,连带PMOS Q1导通,向后输出电压。需要关机时通过发送一个GPIO Switch高电平信号使NMOS Q3导通,C1被充到高电压使得PMOS Q2关断,连带PMOS Q1关断,断电。定时功能主要由R2-C1放电实现。 -

该电路主要考虑以下几个问题:

-

MOS导通电压的分散性。主要针对Q2 Q3。理想状态下Q2工作于数字状态,即C1电压高于某个值,导通,反之关断。但是对于常见的分立MOSFET,导通电压并不固定,如PMOS IRLML6401,导通电压在-0.5V~-0.95V间变化,无法做到理想状态。 -

C1电容的容值变化问题。主要是常见的电容基本都有容值随电压变化而变化的曲线,电压不同导致容值不同,严重影响定时精确性。可用于精确定时场合的电容有C0G材质电容,聚丙烯薄膜电容,电解电容也可以考虑使用 -

各个器件的温漂问题。主要是电阻、电容的器件值会随着温度变化,产生一定的误差。如果采用模拟IC,相关至指标也会随着温度变化,产生额外的误差。

-

给出改进原理图,如下。主要修改的部分是

PMOS Q2开关电路,采用一个迟滞比较器代替。初始时C1电压为0,而比较器同相输入端电压大于0,因此输出高电平,PMOS Q1关断;随着C1电压不断升高,超过同相端电压时,比较器输出低电平,PMOS Q1导通,开机;GPIO Switch发送高电平信号,NMOS Q2导通,C1放电,关机。

-

主要需要设计的参数为电阻

R2、R3比值、时间常数R1*C1以及参考电压Vref。时间关系这里暂时不写设计流程,给出关键值:R3/(R2+R3)=0.2,R1*C1=300,Vref=2.5V,整个电路工作电压设定为3.3V,最后计算出定时关机时间约为907.848s,相对误差为0.88%。 -

注意比较器需要考虑其

输入偏置电流和输入失调电流,因为其输入端的RC电路工作电流很小,较大的输入电流会引起C1电压变化,从而影响定时时间。因此比较器就不采用高速比较器,这种IC为了达到快速响应目的,输入激励要求较高,即输入电流较大。需要采用低输入电流的运放芯片,降低对RC定时电路的影响。这里不需要考虑运放的压摆率,因为输出高电平或低电平的时间都很长,电压翻转时间基本可以忽略不计。

-

-

本文章使用limfx的vscode插件快速发布