AMBA总线

AMBA总线简介

系统芯片中各个模块之间需要有接口来连接

总线作为子系统之间共享的通信链路

优点

低成本

方便易用

缺点

会造成性能瓶颈

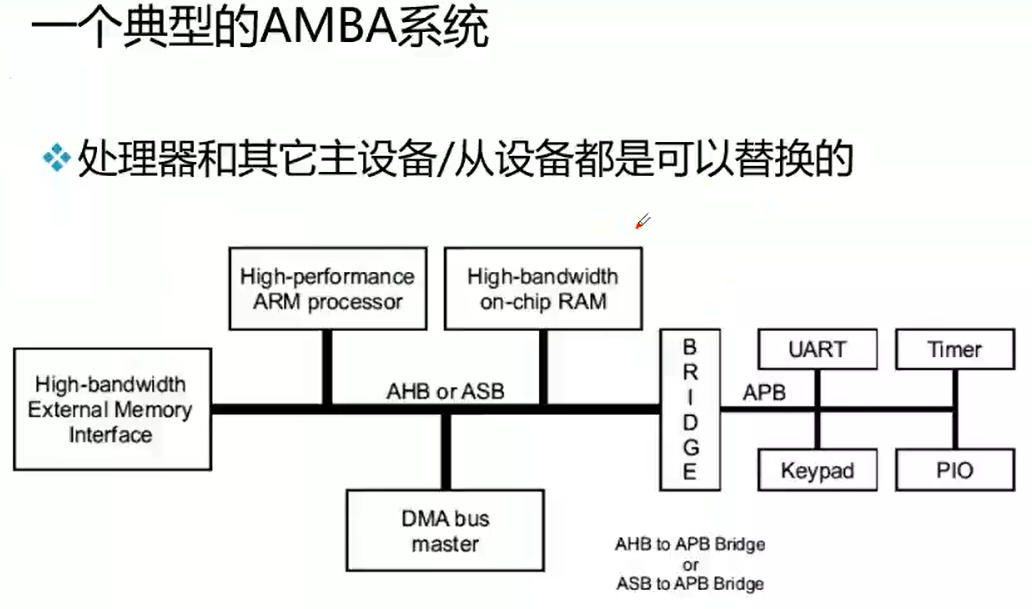

AMBA2.0

片上总线标准

三种总线

AHB 高速100M

ASB

APB 低速20M

典型的AMBA系统

amba总线简单实列

AHB

高速总线,高性能100MHz

2级流水线操作

可支持多个总线主设备(最多16个)

支持burst传输(突发传输)

总线带宽:8、16、32、32、64、128 bits

上升沿触发操作(与工艺有关,电容的充放电实现,电容充电较快,放电比较快,上升沿采样时间短 ,能够容易控制建立时间,保持时间)

对一个新设计建议使用AHB总线

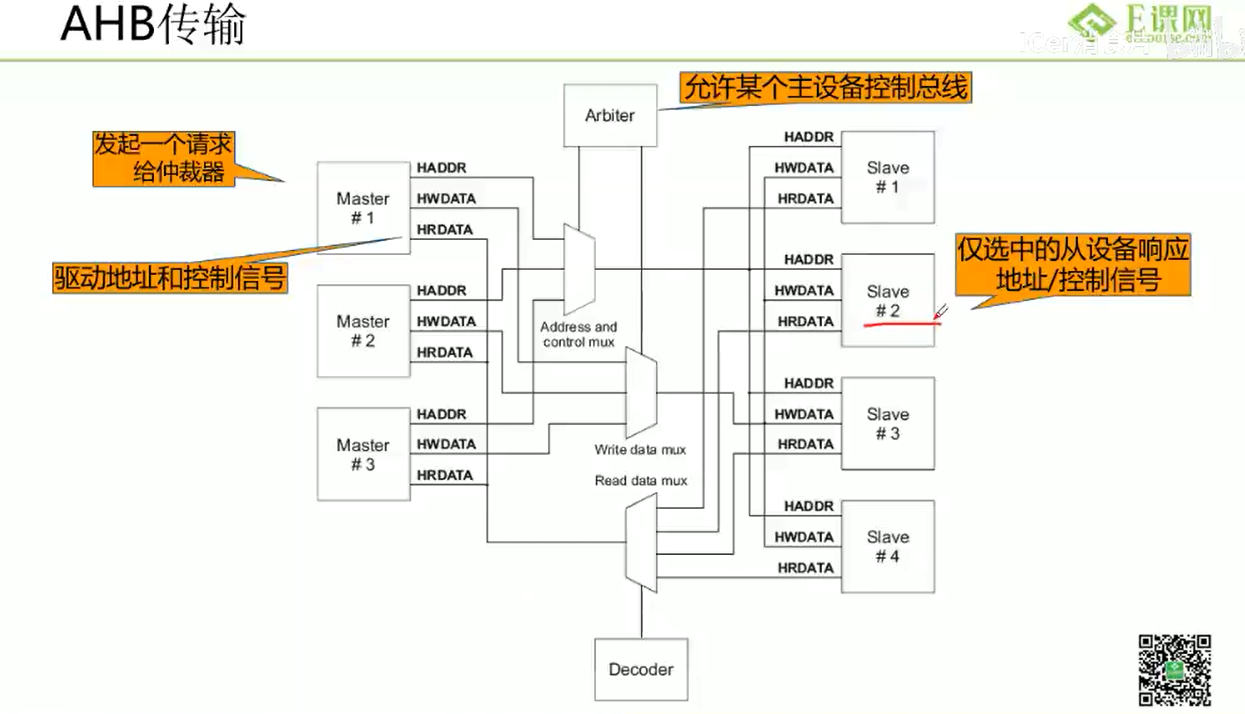

AHB组成部分

AHB主设备(master)

初始化一次读/写操作

某一时刻只允许一个主设备使用总线

CPU、DMA、DSP、LCDC...

AHB从设备(slave)

响应一次读/写操作

通过地址映射来选择哪一个从设备

外部存储器控制EMI、APB Bridge

AHB仲裁器(arbiter)

允许某一主设备控制总线

在AMBA协议中没有定义冲裁算法

AHB译码器(decoder)

通过地址译码器来决定选择哪一个从设备

ASB

高速总线

流水线操作

可支持多个总线主设备

支持burst传输(突发传输)

总线带宽:8、16、32bits

三态、双向总线

不适合做DFT

上升沿或下降沿触发操作(与工艺有关,电容的充放电实现,电容充电较快,放电比较快,上升沿采样时间短 ,能够容易控制建立时间,保持时间)

APB

低速总线,低功耗

接口简单

在Bridge中锁存地址信号和控制信号

适用于多种外设

上升沿触发操作(与工艺有关,电容的充放电实现,电容充电较快,放电比较快,上升沿采样时间短 ,能够容易控制建立时间,保持时间)

APB组成部分

AHB2APB Bridge

可以锁存所有的地址、数据和控制信号

进行二级译码来产生APB从设备选择信号

APB总线上的所有其他模块都是APB从设备

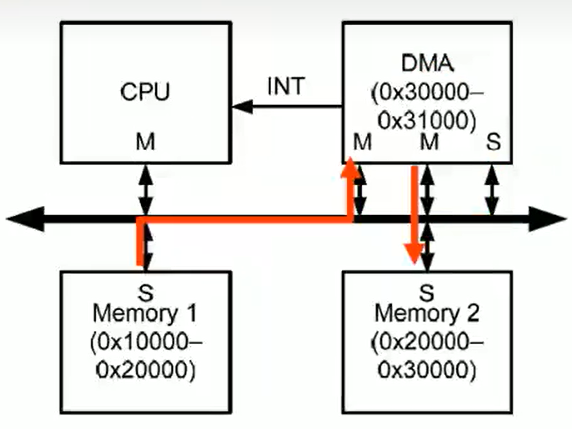

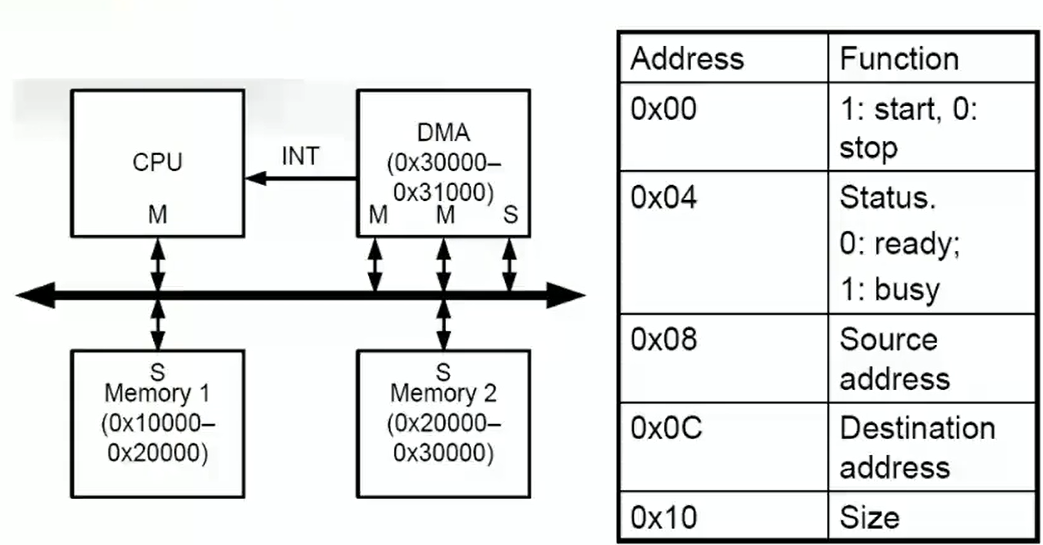

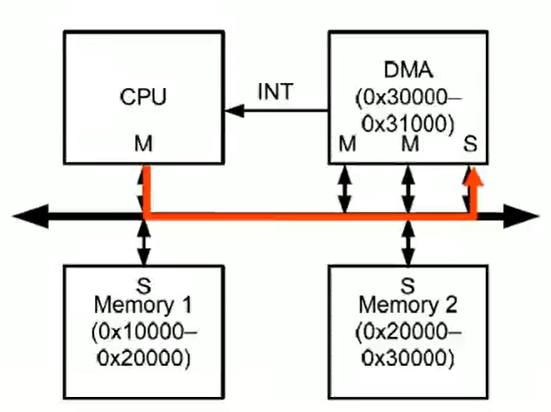

DMA例子

step0:CPU检查DMA的状态以确认是否可用

while(1){ Read(0x30004,&states) if(states==0){ break; } }

step1:CPU设置(source sddress)、(destination address) (size)

write(0x30008,0x10000); write(0x3000C,0x20000); write(0x30010,0x100);

step2:启动DMA

write(0x30000,0x1);

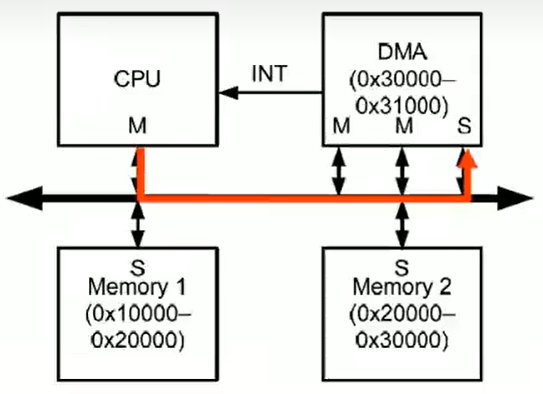

step3:DMA把数据从memory1传送到memory2

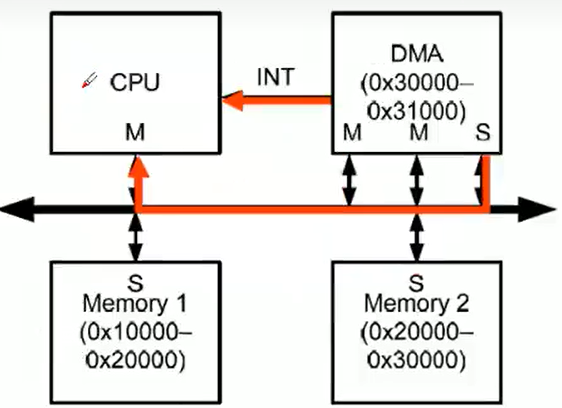

step4:DMA向CPU发出中断请求

step5:CPU检查DMA的状态

Read(0x30004,&status)

总结:CPU查询DMA状态->配置寄存器->启动DMA->DMA开始搬运->DMA搬运完中断CPU->查询

AHB传输

有default master(CPU) default slave Dummy Master (其他master不工作)

每个外设有自己的地址空间

基本AHB信号

HCLK (clock source) BUS clock 总线时钟

HRESETn (reset controller)

低电平有效

HPORT[3:0] (master)

保护控制

HPORT[0]:OPCODE/DATA

HPORT[1]:USER/PRIVILGED

HPORT[2]:Bufferable/Non-Bufferable

HPORT[3]:Cacheable/Non-Cacheable

HADDR[31:0] (master)

32位系统地址总线

HWRITE (master)传输方向,写使能

高电平:写

低电平:读

HWDATA[31:0](master)

写数据总线,从主设备写到从设备

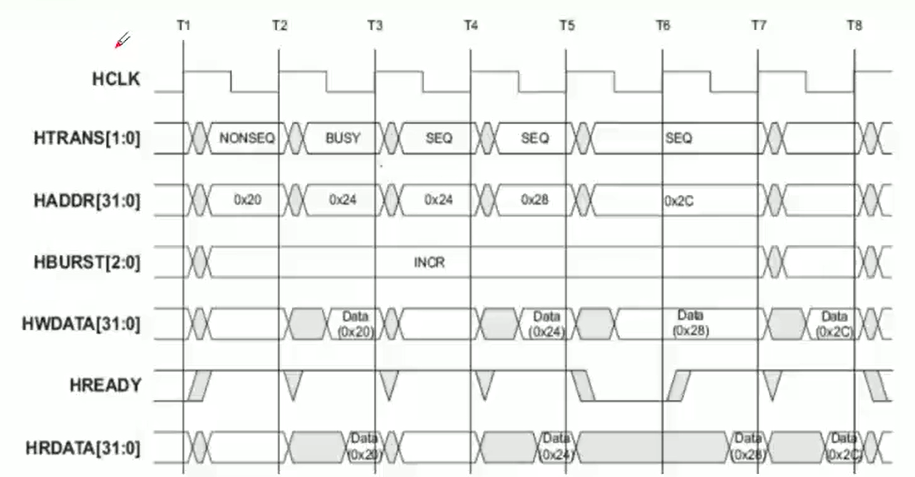

HTRANS (master)

指出当前传输的状态

00 IDLE

主设备占用总线,但没进行传输

两次burst传输中间主设备发IDLE

01 BUSY

主设备占用总线,但是在burst传输过程中还没准备好进行下一次传输

一次burst传输中间主设备发BUSY

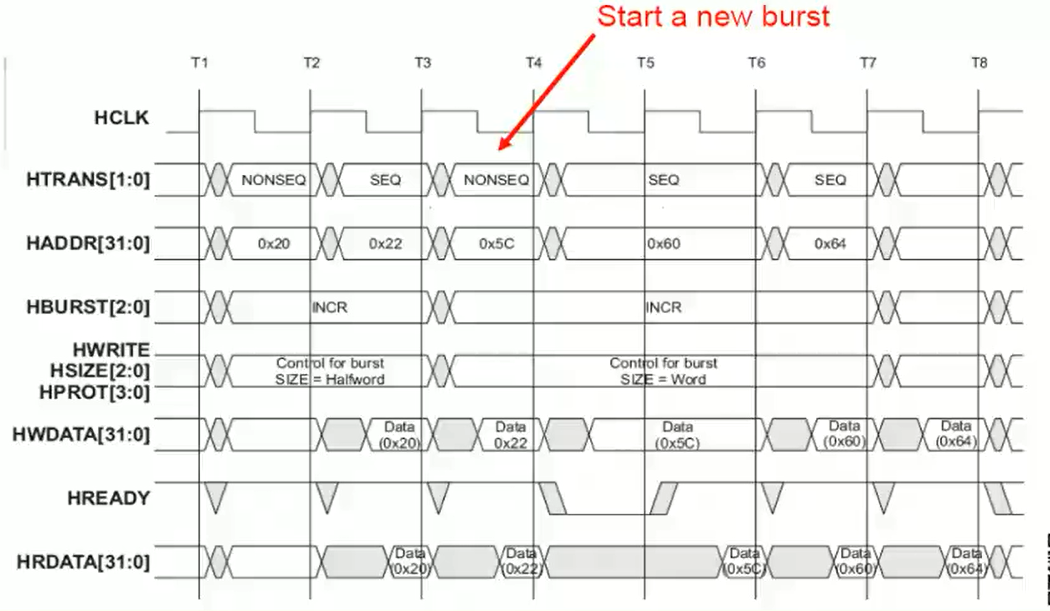

10 NONSEQ

表明一次单个数据的传输

或者一次burst传输的第一个数据

地址和控制信号与上一次传输无关

11 SEQ

表明burst传输接下来的数据

地址和上一次传输的地址相关

HSIZE[2:0] (master)

指出当前传输的大小

000:8bits

001:16bits

010:32bits

011:64bits

100:128bits

101:256bits

110:512bits

111:1024bits

最大值受总线的配置所限制

通常使用32bits(010)

HBURST (master)

指出传输burst类型

不可跨越1K边界

SINGLE

INCR

WRAP[4][8][16]

INCR[4][8][16]

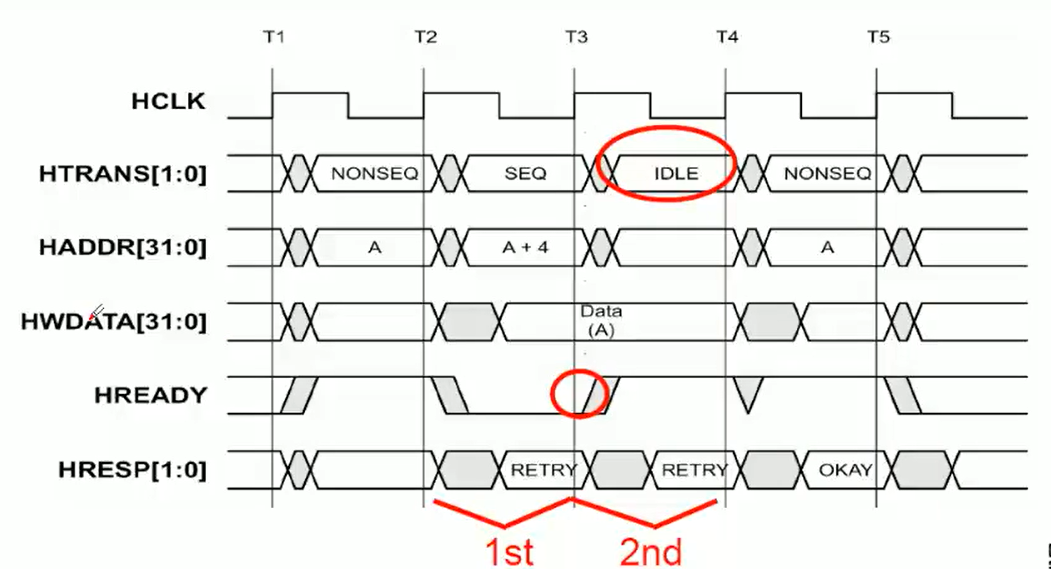

HRESP (slave)

从设备发给主设备的总线传输状态

OKAY、ERROR、RETRY(重传)、SPLIT(分割)

00:OKAY

成功 单周期响应

01:ERROR

失败 两周期响应

10:RETRY

传输未完成 两周期响应

请求主设备重新开始一个传输

11:SPLIT

传输未完成 两周期响应

请求主设备分离一次传输

延迟 分一段传输

HREADY (slave)

高:从设备指出传输结束

低:从设备需延长传输周期

HRDATA[31:0](slave)

读数据总线,从从设备读到主设备

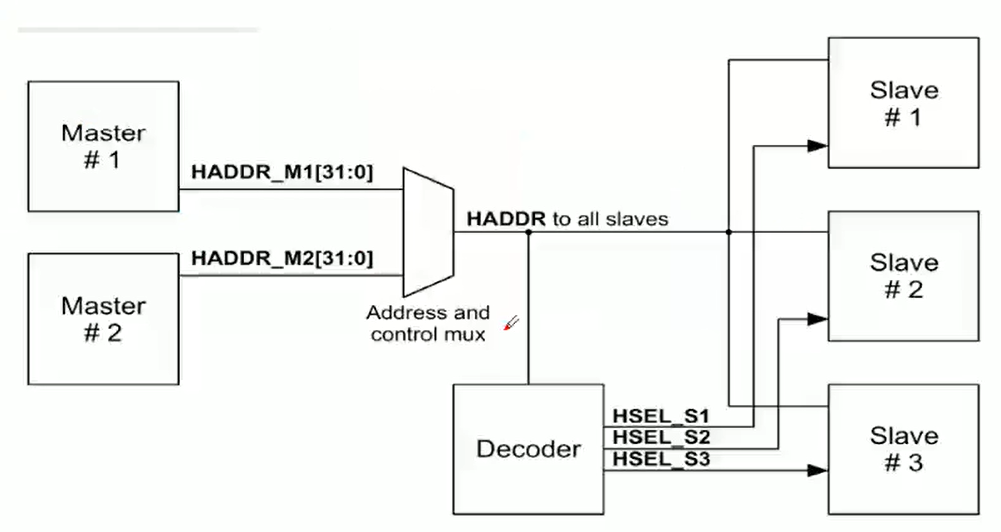

HSELx (Decoder)

读数据总线,从从设备读到主设备

选择从设备

指出由主设备所选择的从设备

由地址译码器来提供所选择的从设备

一个从设备应该至少占用1KB的存储空间

需要额外的缺省从设备来映射其他的存储地址

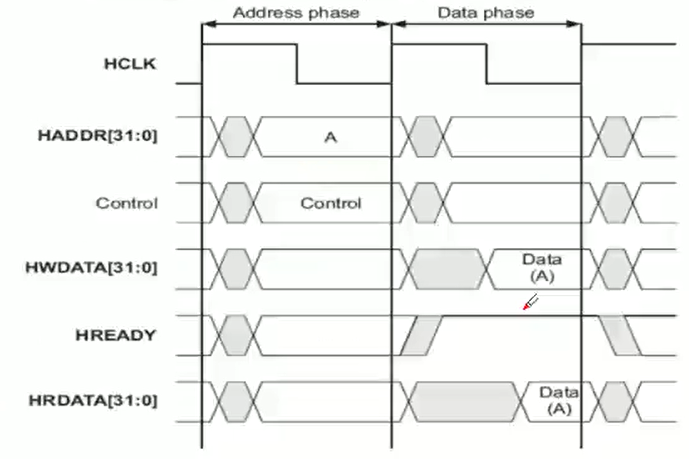

single传输

基本AHB传输

两个阶段

地址周期,只有一个cycle

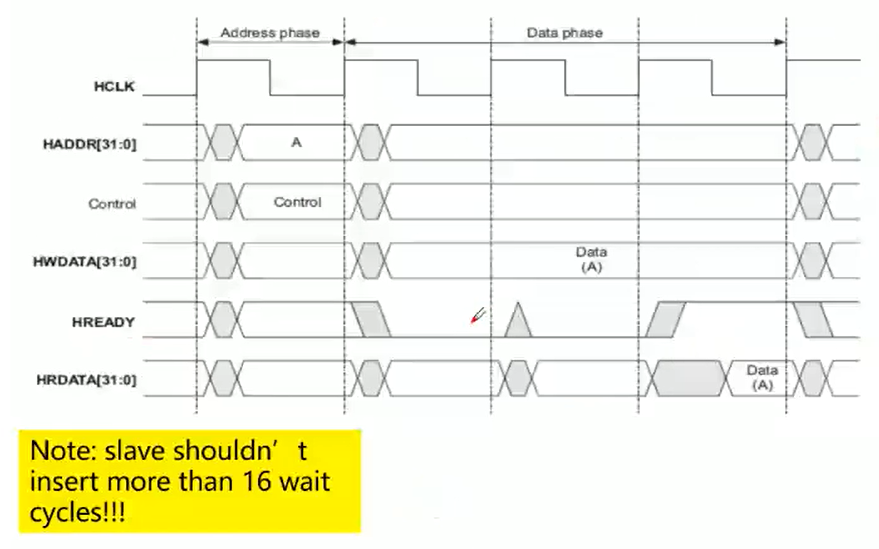

数据周期,由HREADY信号决定需要几个cycle

流水线传送(两拍)

先是地址周期,然后是数据周期

一次无需等待状态的简单传输

一次无需等待简单传输两个周期 ,一个地址周期,一个数据周期

只有当HREADY信号有效时才将数据传输,否则地址保持

需要两个等待周期的简单传输

最多等待16个时钟周期

HREADY为高读到的数据才是对的

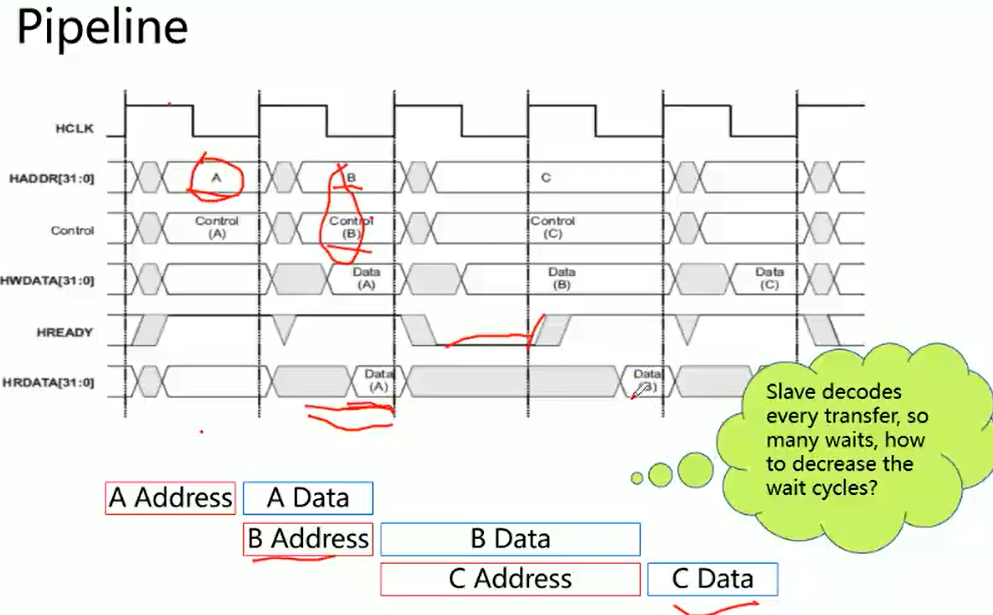

流水线传输

一次传输拆成两个步骤->二级流水线

一次传输拆成三个步骤->三级流水线

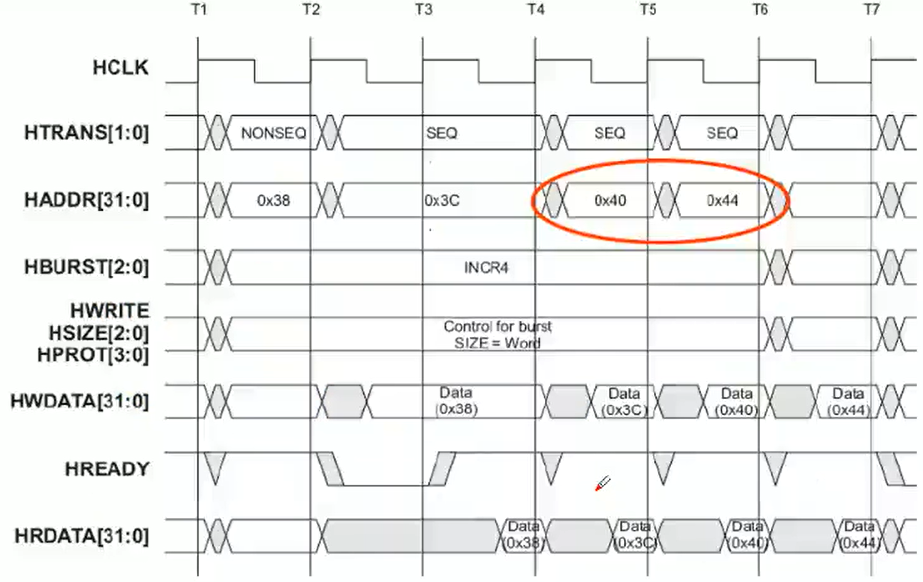

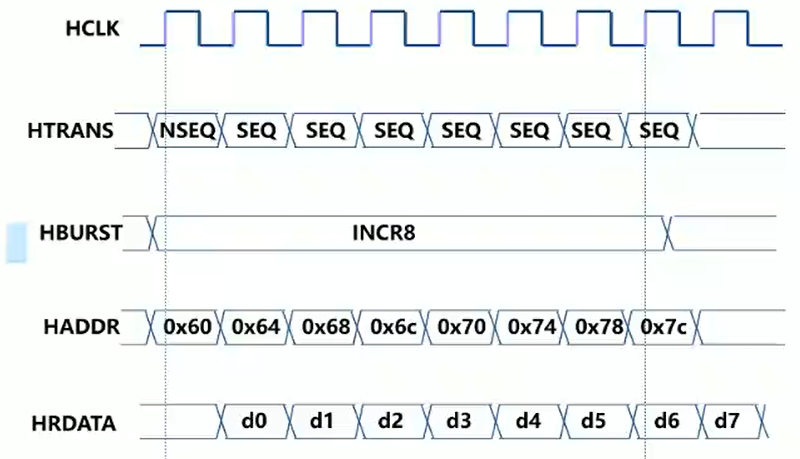

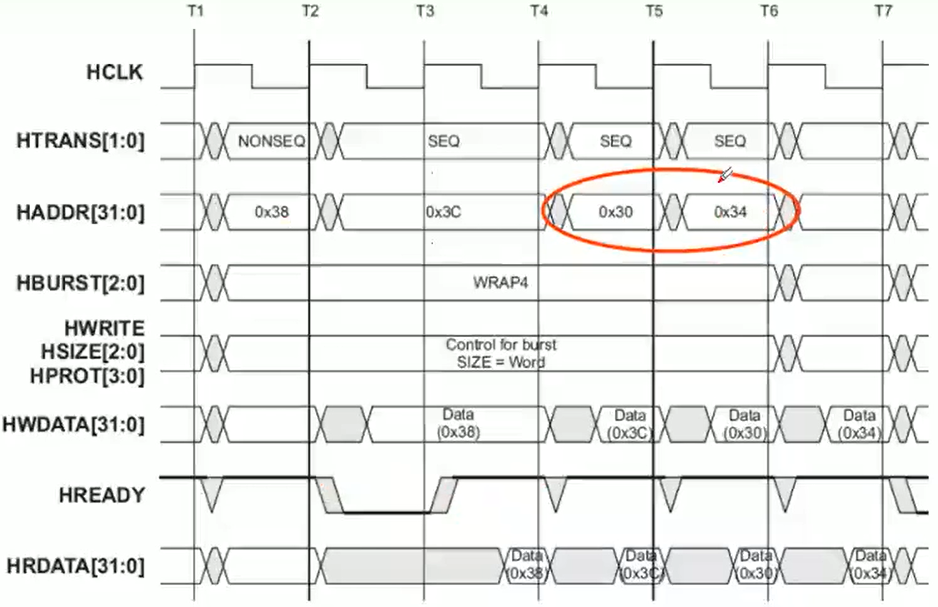

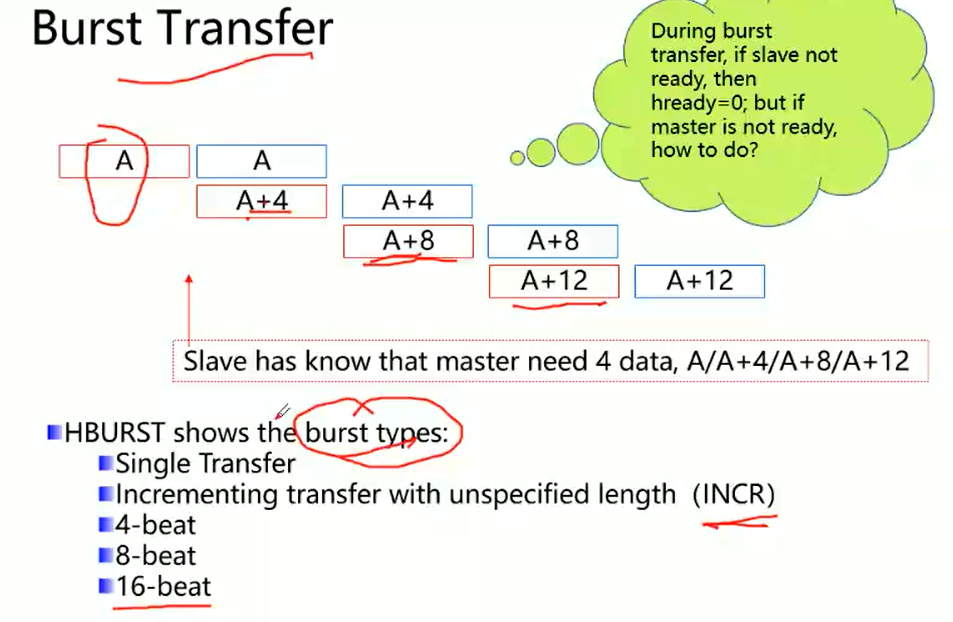

Burst Transfer

single Transfer

incrementing transfer with unspecified length(INCR)

4-beat

8-beat

16-beat

传输类型

例子

例子未定义长度的传输

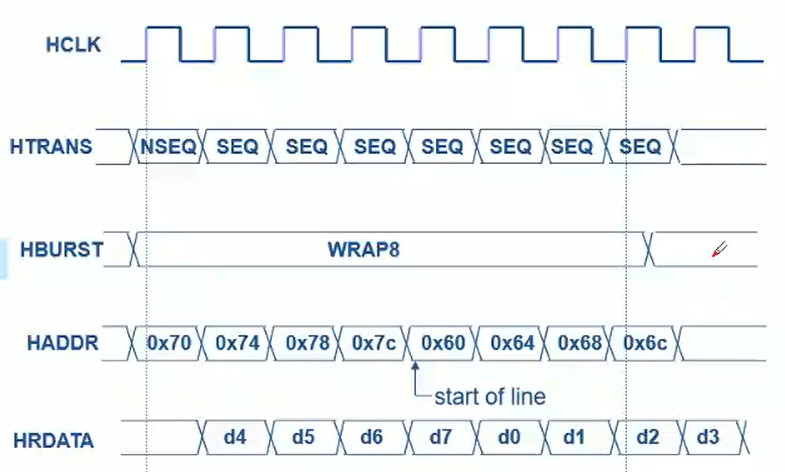

支持incrementing和wrapping两种burst传输

incrementing burst

地址是上一次的传输地址加1

Wrapping burst

4beat的wrapping burst 字传输(4byte)

0x34->0x38->0x3c->0x30

应用场合:Cache填充

根据HSIZE和HBURST来计算地址

例:起始地址是0x48,HSIZE=010(32bits)

INCR4 Burst 4代表四个字节

INCR8 Burst 8代表八个字节

WRAP4 Burst

WRAP8 Burst

未定义长度

HBURST | TYPE | ADDRESS |

|---|---|---|

000 | SINGLE | 0x48 |

001 | INCR | 0x48,0x4C,0x50,... |

010 | WRAP4 | 0x48,0x4C,0x40,0x44 |

011 | INCR4 | 0x48,0x4C,0x50,0x54 |

100 | WRAP8 | 0x48,0x4C,0x50,0x54,0x38,0x3C,0x40,0x44 |

101 | INCR8 | 0x48,0x4C,0x50,0x54,0x58,0x5C,0x60,0x64 |

110 | WRAP16 | 0x48,0x4C,...,0x7C,0x40,0x44 |

111 | INCR16 | 0x48,0x4C,...,0x7C,0x80,0x84 |

地址译码

从设备响应

所访问的从设备必须响应这次传输

从设备可能返回的响应

完成这次传输

插入等待状态(HREADY信号)

发出错误信号表示这次传输失败

延迟传输,使得总线可用于其他传输(split)

总线的流水特性需要从设备两个周期的响应。可以使得主设备有足够的时间处理下一次传输

retry响应

RETRY和SPLIT的区别

主要区别在于仲裁的方式

RETRY:arbiter会继续使用通常的优先级

SPLIT:arbiter会调整优先级方案以便其他请求总线的主设备可以访问总线

总线主设备应以同样的方式处理RETRY响应和SPLIT响应

数据总线

不是三态总线,读总线和写总线是分开的

印第安序(数据模式,大端对齐还是小端对齐)

在AMBA协议中没有定义

主设备和从设备应该采用同样的印第安序

不支持动态的印第安序

32bits小端对齐

32bits 大端对齐

对于IP设计,只有应用面比较广泛的应用程序才支持两种印第安序

AHB仲裁器

AHB仲裁信号

Name | Source | Description |

|---|---|---|

HBUSRWQx | Master | Bus request |

HLOCKx | Master | Locked transfers |

HGRANT | Arbiter | Bus grant |

HMASTER[3:0] | Arbiter | Master number |

HMASTLOCK | Arbiter | Locked sequence |

HSPLITx[15:0] | Slave(SPLIT-capable) | Split completion request |

HBUSRWQx

总线请求

HLOCKx

高电平:主设备请求锁定总线

HGRANT

指出主设备x可访问总线

主设备x控制总线:HGRANTx=1且HREADY=1

HMASTER[3:0]

指出哪个设备正在进行传输

4位16个

HMASTLOCK

指出主设备正在进行一次锁定传输

HSPLITx[15:0]

从设备用这个信号告诉仲裁器哪个主设备允许重新尝试一次split传输

每一位对应一个主设备

仲裁举例

无等待状态的grant

有等待状态的grant

AHB主设备接口

AHB从设备接口

仲裁器Arbiter

AHB Decoder

多层

AHB Lite简化版

AHB总结

主要组成部分

MASTER SLAVE ARBITER DECODER

传输的过程

流水线机制

Address phase和data phase

如何提高性能

Burst read/write

仲裁机制

总线控制权的移交

slave短时间内无法响应

HREADY信号拉低

slave长时间内无法响应

插入SPLIT/RETRY

MASTER长不能进行传输

插入BUSY

AHB应用建议

Arbiter 的优先级可以配置

Slave长时间不能响应的话,一般不支持SPLIT响应,使用RETRY响应

总线上如果只有一个master的话,可以使用AHB lite协议,不使用arbiter

设计一个新的IP时,要仔细核对AMBA的Feature和IP所支持的Feature是否匹配。

实现

DMA

DMA

APB

通过BRIDGE连接

APB信号

| name | description |

| ----------- | ---------------------- |

| PCLK | Bus clock |

| PRESETn | APB reset |

| PADDR[31:0] | APB address bus |

| PSELx | APB select |

| PENABLE | APB strobe |

| PWRITE | APB TRANSFER direction |

| PRDATA | APB read data bus |

| PWDATA | APB write data bus |PADDR[31:0]

地址总线,由设备总线的bridge单元驱动

PSELx

从译码器来的信号,到每一个总线从设备x

PENABLE

用于在设备总线上把所有访问按时间阶段进行

PWRITE

高电平:写

低电平:读

PRDATA和PWDATA

最多32位宽

地址映射

AHB->AHB BRIDGE->APB设备(两级映射)

APB读写传输

写传输

读传输

BRIDGE

BRIDGE FSM (实现两级流水)

APB SLAVE

APB到AHB的接口--读

不同IP之间的互联

CPU(master)<--->IP(slave)

IP(master) <--->IP(slave)

Memory mapped io

每个从设备都占用系统中的一段地址空间

所有的从设备都是可寻址的

寄存器/存储器都是内存映射方式访问

CPU/IP读写其他ip的数据类似于读写寄存器

主设备被arbiter grant之后,都可以访问总线上的所有从设备

一个ip可以同时拥有主设备和从设备接口(DMA)

CPU和IP之间的通信

总结

AMBA简介

AMBA2.0 :AHB、ASB、APB

AHB的组成部分

master slave arbiter decoder

APB的组成部分

AHB2APB bridge、APB Slave

AHB信号

HCLK HRESETn HADDR HTRANS HWRITE HSIZE HBURST HEDATA HSELx HRDATA HREADY HRESP

AHB 传输的两个阶段

地址周期、数据周期

当前传输的状态HTRANS

IDLE、BUSY、NONSEQ、SEQ

突发传输的类型HBURST

SINGLE、INCR(如何开始一次新的incr?(nonseq))

Burst传输不可跨越1K边界

HSEL:由AHB decoder通过地址映射给出

AHB SLAVE 响应信号:

HREADY传输完成、HRESP传输响应(OK、ERROR、RETRY)

AHB slave短时间无法响应?(HREADY拉低)长时间无法响应(RETRY SPLIT)

32bit小端模式,数据总线的有效字节序

AHB仲裁信号

HBUSREQ、HGRANT、HMASTER

主设备x可控制总线条件

AHB master、AHB slave、AHB arbiter、AHB decoder的接口信号

AHB Lite

APB信号

PCLK PRESET PADDR PSEL PENABLE PWARITE PRDATE PWDATA

APB slave 的地址映射

APB传输

Always rwo cycle transfer:Setup cycle、enable cycle

No wait cycle and response signal

APB bridge 和APB slave的接口信号

本文章使用limfx的vscode插件快速发布