DirectDAQ整体设计方案

整体设计方案

主控部分

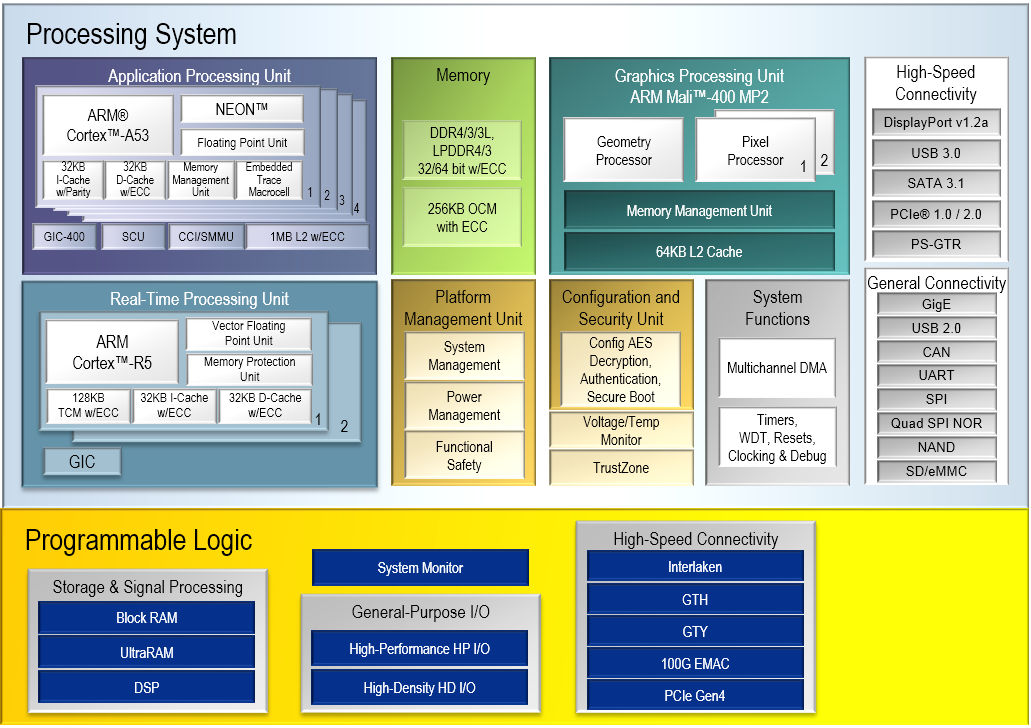

主控采用Zynq UtrlaScale+ MPSoC,具体型号为XCZU7EG,具体框图如下。在本次设计中主要使用的是其ARM Cortex-A53和Prgrammable Logic。PL侧具备PCIe硬核,最高支持 Gen3,PS侧同样具备PCIe硬核,最高支持Gen2。受限于型号,本次主控型号中PCIe无法支持Gen4。

实时传输

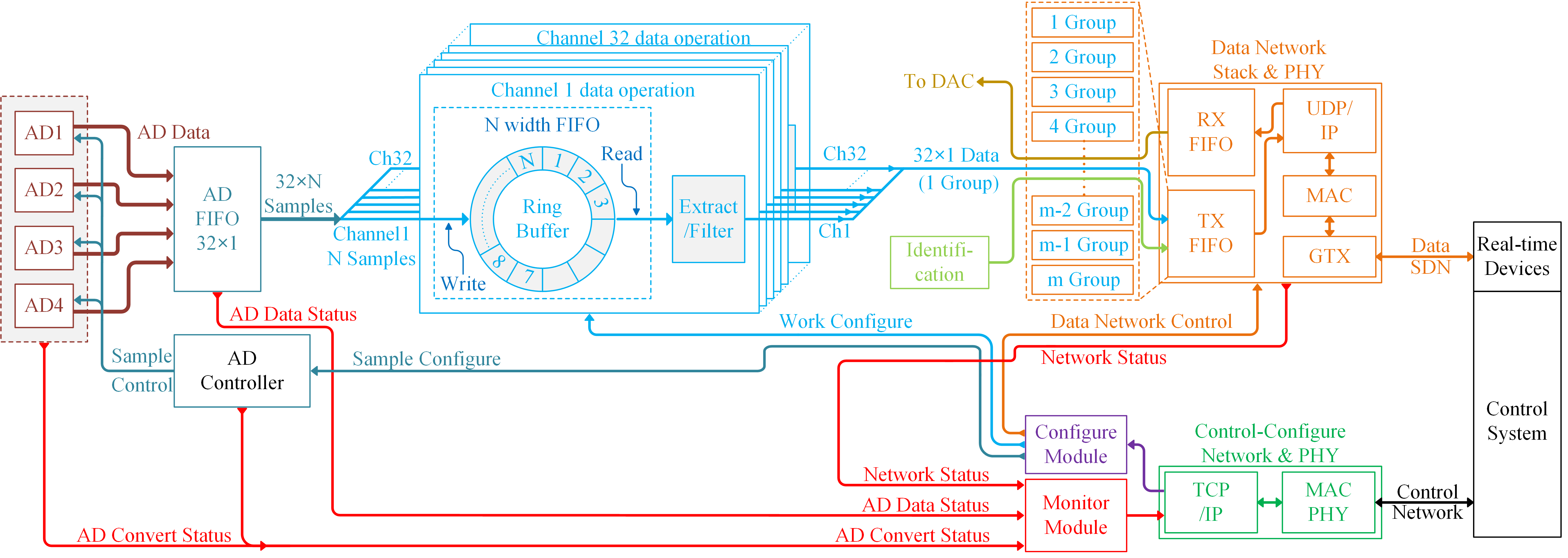

目前设计的结构如下。

- 数据抽取采用一个N宽度的FIFO,可以为

Ping-Pong FIFO或Ring FIFO,采用一个数据读取计数器,采用计数器进行数据抽取。数据网络在PL侧进行,基于GTX/GTH进行网络传输。 Cortex-A内核上运行Linux系统,采用TCP/IP进行整个系统的关键参数配置和状态监控。参数配置包括AD采样配置、数据抽取配置、数据传输网络参数配置;状态监控包括AD采样状态监控、数据状态监控、网络传输状态监控等。

数据存储

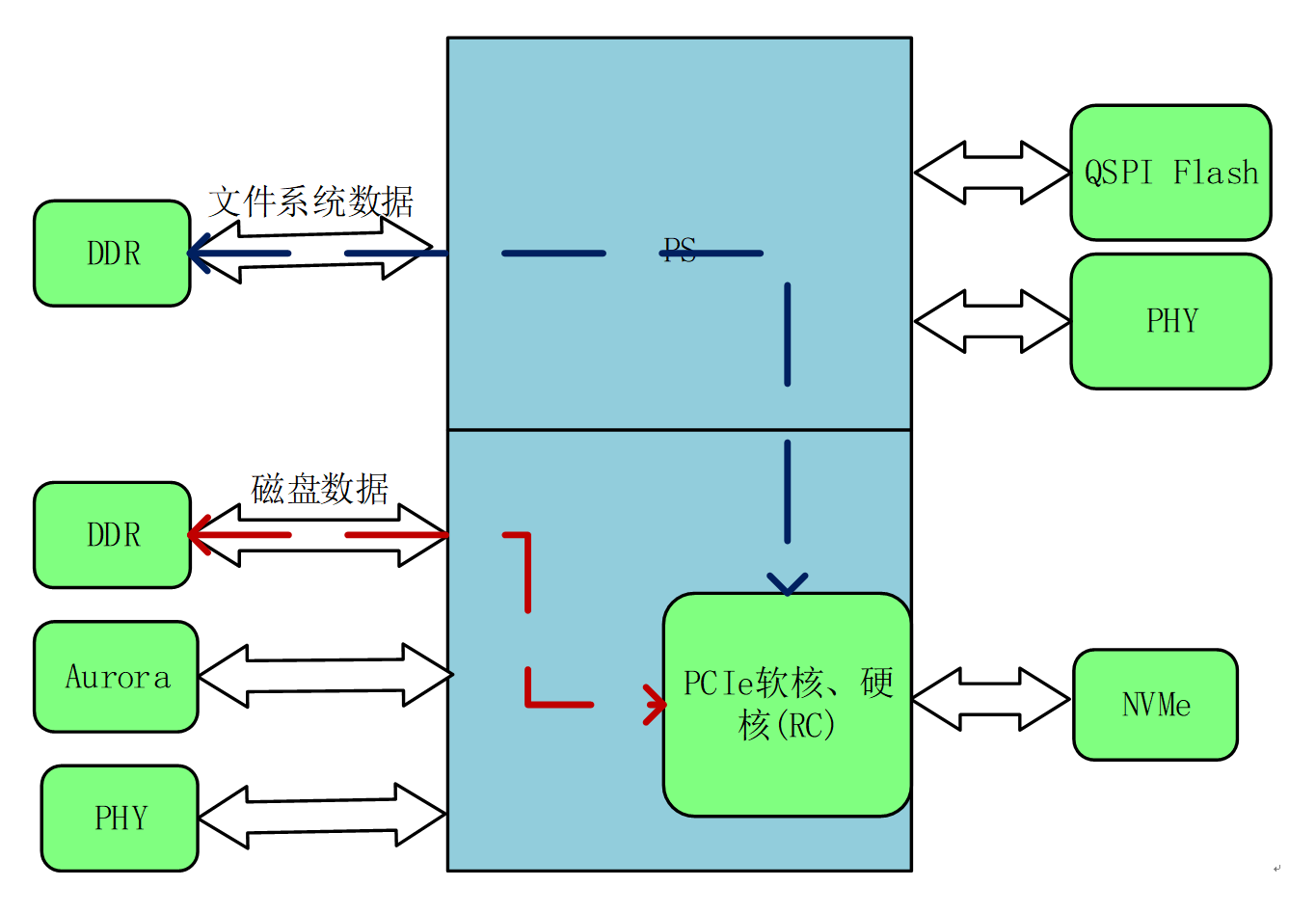

采用ZYNQ实现NVMe主要原因在于ZYNQ具有cortex-A内核,可以运行Linux系统。NVMe的读写需要软硬件配合,采用ARM+FPGA异构的ZYNQ最为合适。国产也有相关的IC代替ZYNQ,如复旦微的FMQL45T900。

PS侧与PL侧具有4个高性能(HP)AXI接口,可双向读写。 其中,PL侧为主机侧(Master),PS侧为从机侧(Slave)。

具体方案:

-

全PS侧操作。ADC数据通过HP-AXI写入PS侧DDR,PS侧采用软件完成SSD的全部操作,主要为将采集数据在SSD中的读写,以及SSD文件系统的构建。

-

PL+PS操作。具体见:http://www.levelchip.com/Content/2266735.html,即 ZYNQ+NVMe 小型化存储解决方案。PL侧需要用硬件构建NVMe控制器和PCIe控制器,PS侧需要用软件构建NVMe磁盘软件驱动、EXT4文件系统。

本文章使用limfx的vscode插件快速发布