AD板卡设计

AD Board 设计

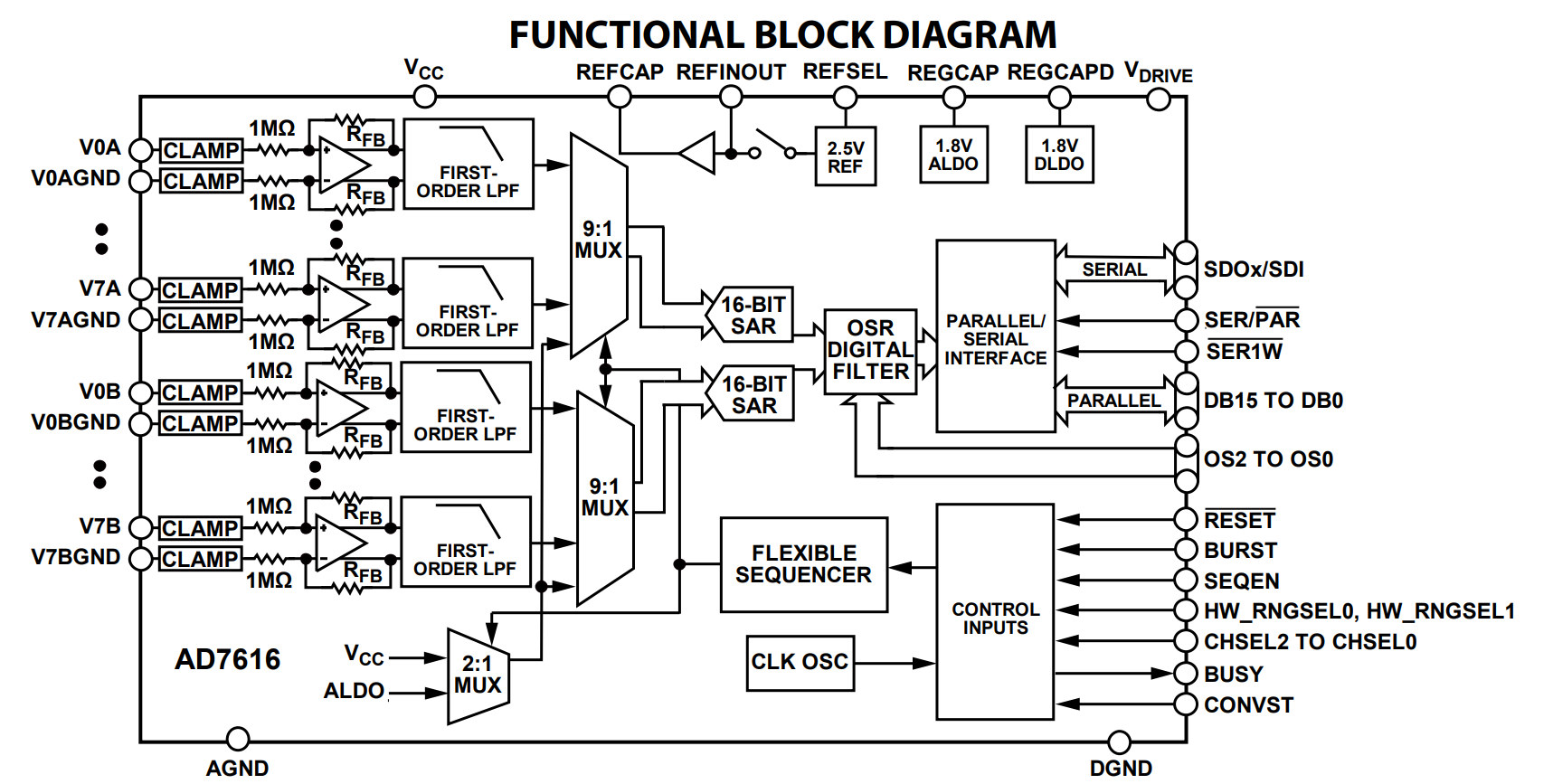

ADC芯片:原来采用AD7616

AD7616功能框图如下,主要对

SEQEN、SER/PAR等引脚进行配置。

具体配置如下:

SER/PAR:串行或并行选择,这里选择并行。串行下数据采用2线、50MHz输出,无法跑满AD7616的完整带宽。并行采用16位输出,没有以上问题。

SER1W:并行下该引脚位 DB4,无需配置。

OS0-OS2:过采样控制,允许过采样提高分辨率,目前不需要。

HW_RNGSEL0、HW_RNGSEL1:软件/硬件模式选择与输入范围设定。

HW_RNGSELx = 00:软件模式,不采用。

HW_RNGSELx = 01:硬件模式,模拟输入范围为 ±2.5V;

HW_RNGSELx = 10:硬件模式,模拟输入范围为 ±5V;

HW_RNGSELx = 11:硬件模式,模拟输入范围为 ±10V.

目前确定采用硬件模式,对于模拟输入的范围拟采用拨码开关的形式进行设定。

SWQEN:序列器使能,用于控制转换通道的顺序,即使能序列器后转换开始时,从V0x通道开始,到设定的通道结束。确定使能序列器。

CHSEL0-CHSEL0:设定序列器结束通道,按照3bits数进行设定。

BURST:突发,硬件模式下使能BURST功能,则一个序列中仅需要一个CONVST脉冲即可开始所有通道的转换,否则每进行一个通道的转换,都需要一个CONVST脉冲。

深入对AD7616进行分析后发现,AD7616对多通道进行采样的方式为每个通道都进行ACQ-CONVST模式,即先采样后转换的模式。由于输入采用9:1的MUX,对比7606,AD7616输入缺少统一T/H电路,因此每对一个通道进行转换时就必须先采集后转换,使得每个部分内的8个通道转换共享 1M的采样率,即一对通达1M,4对通道则为250k,8对则为125k。

对于以上问题,具有2M、16通道的同步采样卡PXIe-6368是采用16个2M ADC、在转换开始信号上做同步实现的。

对于每个通道都需要1M的采样率,目前需要更换芯片,可采用的芯片有AD7606C-16、LTC2324-16,主要特性:

AD7606C-16:8通道,每通道1M,16bits,8线串行或16位并行输出;

LTC2324-16:4通道,每通道2M,16bits,4线串行输出。

ADC拟采用LTC2324-16,则需要设计其前端驱动电路,主要为增益变换、衰减和抗混叠部分。前端电路的输入输出均采用差分形式设计,输入为±10V或±5V。

LTC2324-16的IO输出部分支持1.8V电压,可以直接与FPGA 1.8V BankIO 对接,无需IO电压转换。

所有模拟信号输入:VHDCI68,由于不是通用型器件,需要自行在 AD 中绘制封装。VHDCI68接口物理长度为41.9cm。

AD Borad 尺寸:主要受到 1U 机箱的限制,需要进行划分。1U 机箱横向长度约42cm,则单个AD板卡最大可以长度可以支持到约10cm。考虑到空间利用,暂定单个AD板的长度为8cm,纵向长度视设计而定。

本文章使用limfx的vscode插件快速发布