UDP RGMII 千兆以太网思考方案

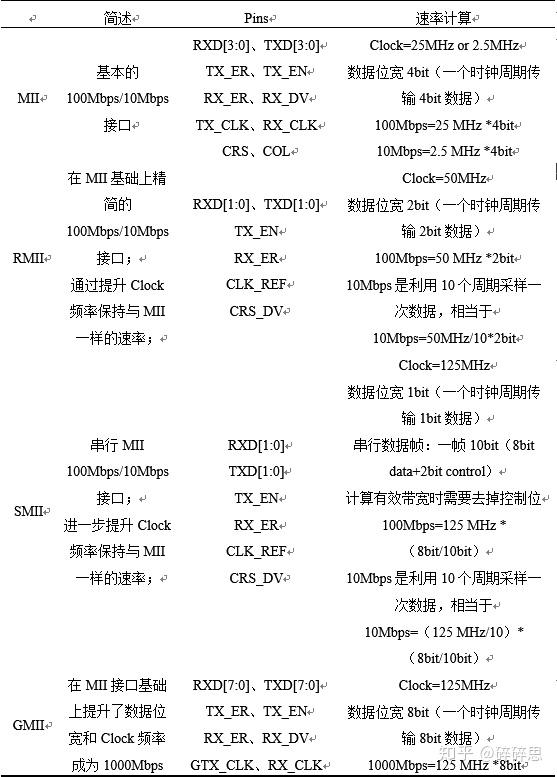

以太网MII接口

MII是英文 Medium Independent Interface 的缩写,翻译成中文是“介质独立接口”,该接口一般应用于以太网硬件平台的MAC层和PHY层之间,MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII、TBI、RTBI、XGMII、XAUI、XLAUI等。

RGMII的主要优势在于,它可同时适用于 1000M、 100M、 10M 三种速率,我们版上的硬件接口也是RGMII接口

RGMII信号定义

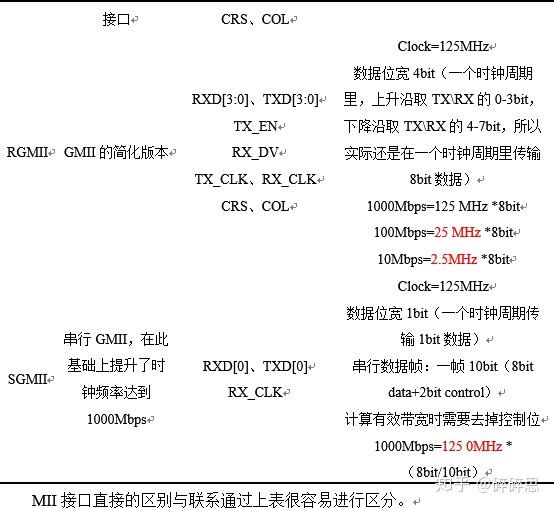

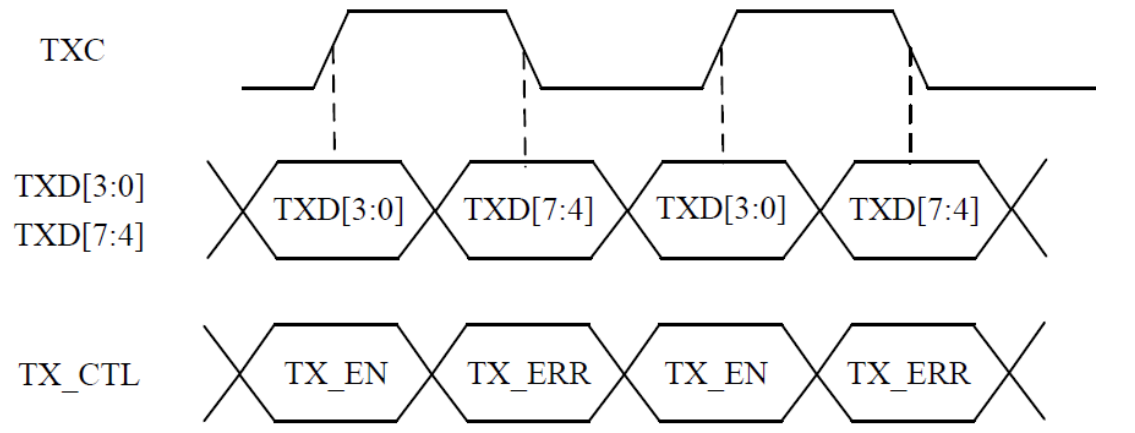

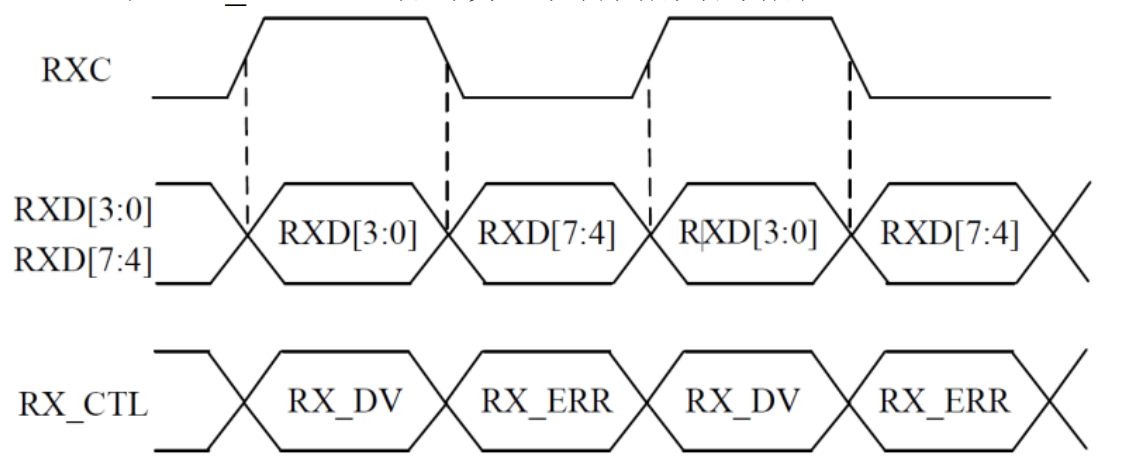

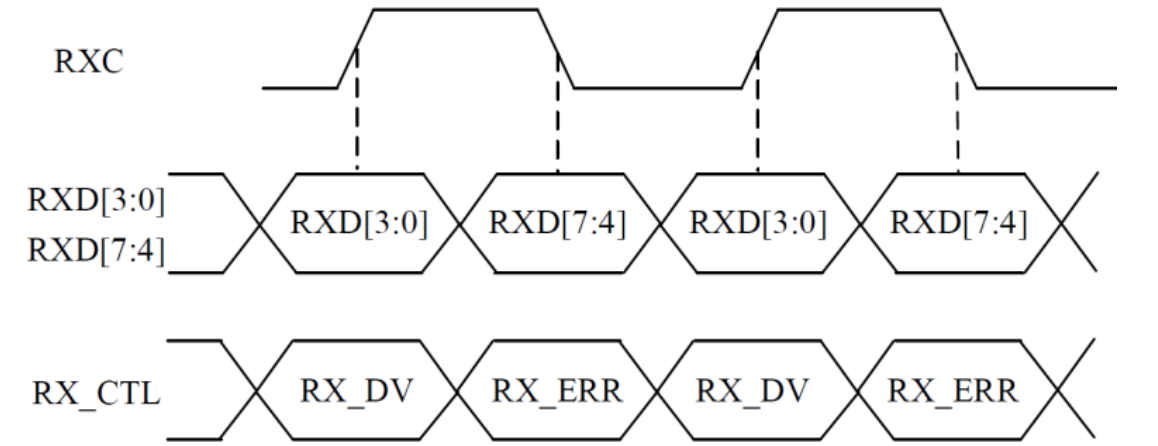

RGMII 使用 4bit 数据接口采用上下沿 DDR(Double Data Rate)的方式在一个时钟周期内传输 8bit 数据信号,即上升沿发送或者接收数据的低 4 位[3:0],下降沿发送或者接收数据的高 4 位[7:4]。

同理,使用 1bit 控制接口采用 DDR的方式在一个时钟周期内传输 2bit 控制信号,即在上升沿发送或者接收数据使能信号(TX_EN、RX_DV),下降沿发送数据错误信号与使能信号的逻辑异戒值(TX_ERR xor TX_EN、RX_ERR xor RX_DV),根据该信号可以计算出相应的数据错误信号。

发送端:

-

TXC:发送数据信号和控制信号对应的同步时钟信号(125M、25M、2.5M)

-

TXD[3:0]:发送数据信号, 4bit 位宽

-

TX_CTL:发送控制信号

接收端:

-

RXC:接收数据信号和控制信号对应的同步时钟信号(125M、25M、2.5M)

-

RXD[3:0]:接收数据信号,4bit 位宽

-

RX_CTL:接收控制信号

时序要求

发送端:

一般的 PHY 芯片都支持两种 RGMII 发送端口的时序关系。

一种称为非延时模式,如下图所示。

TXC 比其他信号存在 2ns(90°相位)左右的延时。

另一种为延时模式,如下图所示。

接收端:

非延时如下图所示。

延时模式时序关系如下图所示。

一般来说,PHY 芯片默认即可能是延时模式也有可能是非延时模式,可通过 MDIO 接口设置相应的寄存器,或者芯片特殊功能引脚改变 PHY 芯片的 RGMII 接口时序模式。

如果使用一个PHY芯片的默认时序的话,就要确认时延时还是非延时,然后确认时钟是否需要加相位90°

米联客UDP通信架构

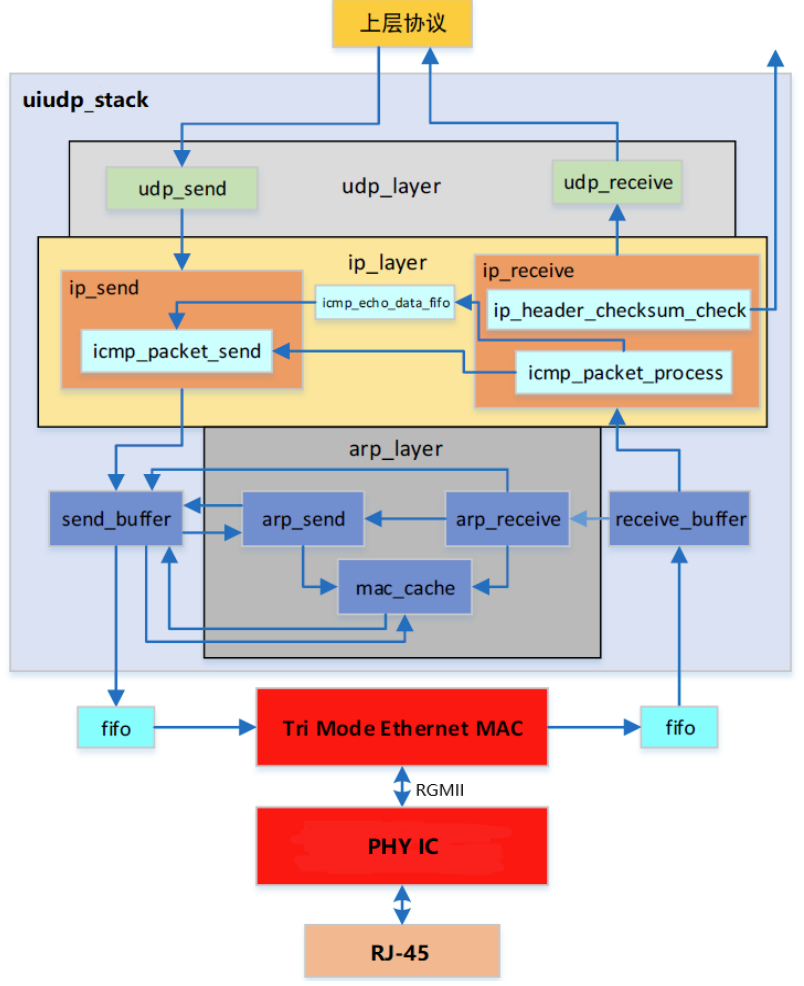

uiudp_stack 这里对于用户就是一个“黑盒子”,上层协议就是用户实际收发的有效数据部分,而 Tri Mode Ethernet MAC 负责处理以太网的 MAC,以及通过 RGMII 接口和 RGMII 接口的 PHY 芯片通信。

米联客udp方案如下图所示

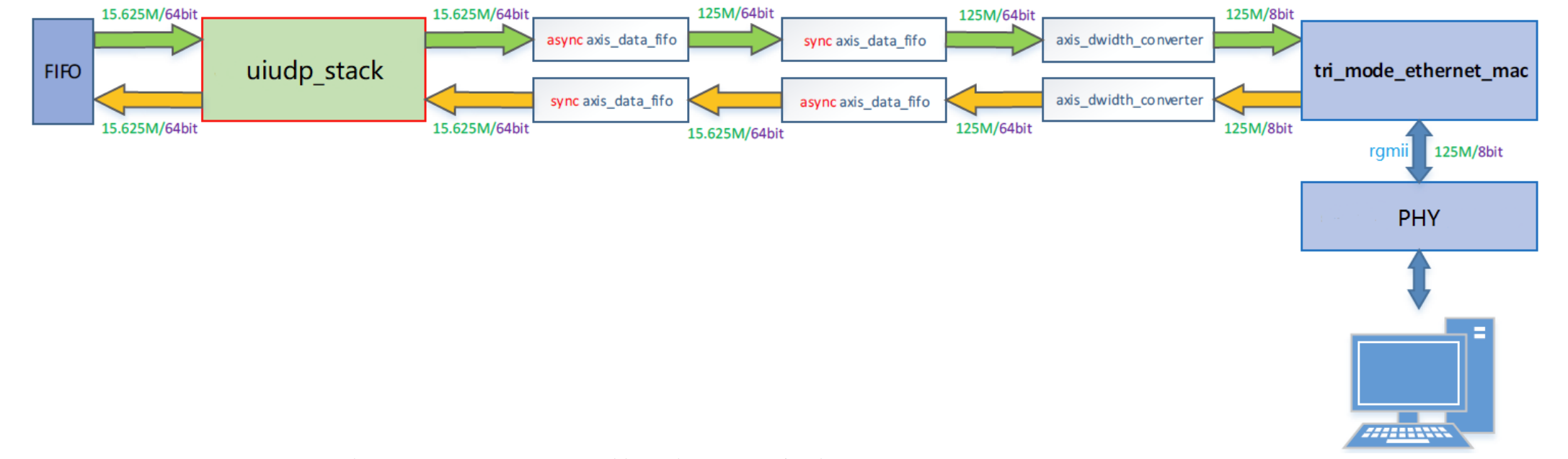

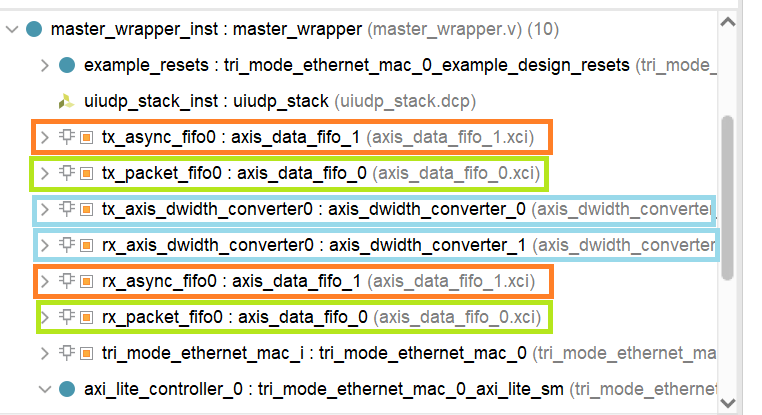

项目的架构如下所示

其中uiudp_stack完成了udp,ip,arp三重功能

async_fifo的功能是将数据跨时钟域传输

packet_fifo的功能是实现数据缓冲和同步Packet mode

AXI4-Stream Data Width Converter的功能是数据位宽转换

Tri Mode Ethernet MAC是VIVADO提供的IP核,需要配置

但IP核的使用需要向amd公司付费,故放弃使用该方案

verilog-ethernet

网上也有开源的udp方案,其中之一是verilog-ethernet

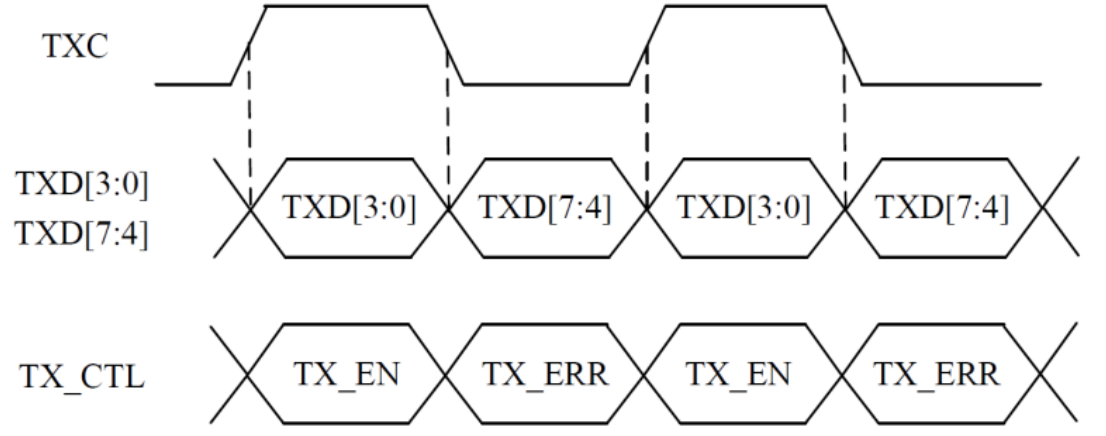

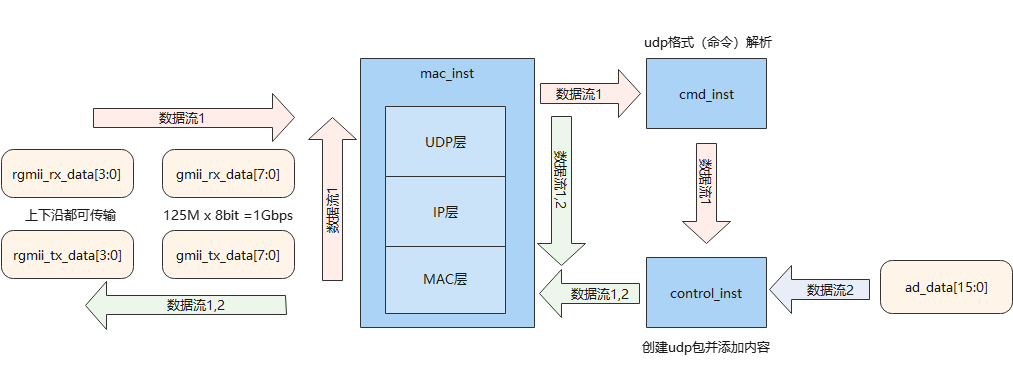

ad_ethernet数据流向

这是我个人参考其他项目以及思考得到的ad采集千兆以太网传输方案的数据流向

图中有两个数据流:

数据流1表示上位机发出的udp包被fpga接收并解析,路径为:

RJ45->rgmii_rx_data->gmii_rx_data->

mac_inst_mac层->mac_inst_ip层->mac_inst_udp层->

cmd_inst->control_inst->

mac_inst_udp层->mac_inst_ip层->mac_inst_mac层->

gmii_tx_data->rgmii_tx_data->RJ45

数据流2表示fpga将采集到的16位ad信号封装成udp包并发送,路径为:

ad_data->control_inst->

mac_inst_udp层->mac_inst_ip层->mac_inst_mac层->

gmii_tx_data->rgmii_tx_data->RJ45

mac_inst负责udp包的装包和拆包,或者说向上传递和向下传递

cmd_inst负责解析fpga收到的udp包,并传递数据进行下一步控制

control_inst根据cmd_inst的数据或采集到的ad数据确定发送的udp包,并交付给mac_inst

本文章使用limfx的vscode插件快速发布