AD子卡设计

AD板卡设计

-

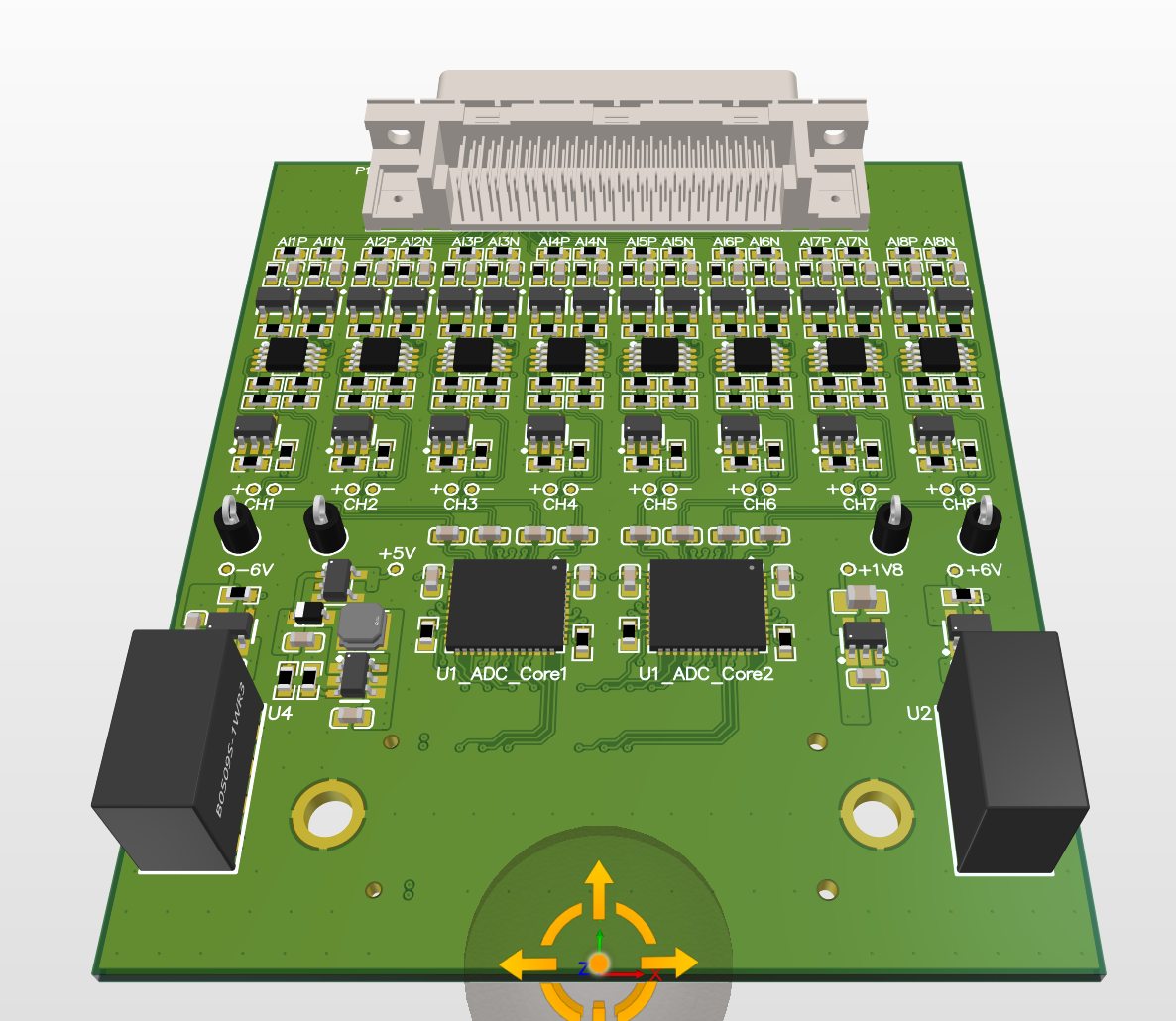

已经完成AD采集板卡的设计,如下。

-

主要特性如下:

-

支持8路模拟输入,单端输入或差分输入自兼容。

-

差分输入支持 ±10V(IN+至IN-),单端输入支持 ±5V(IN+或IN-至GND)。

-

差分输入阻抗为 4MΩ,共模输入阻抗为 1MΩ。

-

模拟输入带宽(-3dB)约560kHz。

-

尺寸:板卡尺寸(不包含VHDCI-68接口,仅PCB)为61mm x 71mm。

-

保护功能:单个输入端(对GND)最高支持约 ±20V 耐压保护。

-

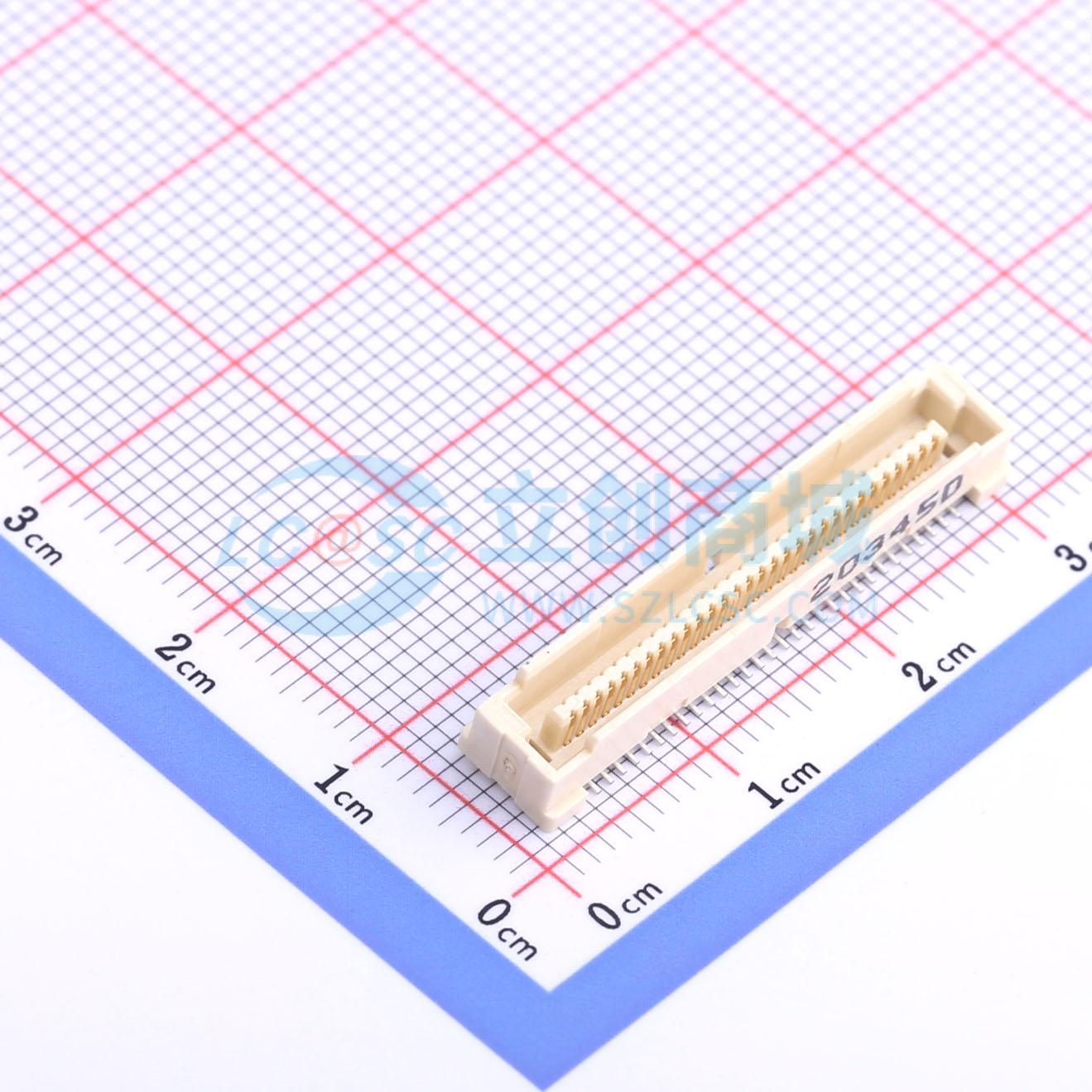

物理接口:模拟输入接口为VHDCI68,数字输入输出接口为2x 5177984-2-60Pin(molex\TE)型接口。

-

数据接口:数字输入输出接口与FPGA对接,目前FPGA核心板上可使用约48对差分接口,给每个数据接口可分配约12对差分接口,足够支持

更高采样率或更高分辨率或更多通道数的AD子卡。另外考虑可以将GTH引入数据接口中,可支持JESD204B型ADC。

-

ADC相关设计

- ADC采用两块 LTC-2324 ADC,工作模式设定为回波模式。

-

回波模式下数据读取时钟由ADC根据FPGA输出的SPI时钟提供,数据边沿与回波时钟具有匹配的边沿,可减小数据读取的驱动时钟的时序要求。

-

ADI官方给出的例程中采用FPGA自行生成数据读取驱动时钟,采用EP3C PLL生成多路时钟后进行组合,主要为匹配数据读取时钟和数据边沿的延时。Xilinx FPGA不具备 EP3C PLL的调节时钟占空比功能,故无法使用例程方法。

-

FPGA端数据读取流程:回波时钟驱动下读取16bits数据,采用移位寄存器对数据进行暂存。15次移位后表示数据读取完成,将移位寄存器中数据搬运到采样数据寄存器中,完成数据读取。

-

CNV信号生成:本应用对于CNV信号的低电平抖动要求不高,可以采用FPGA直接输出。CNV下降沿驱动ADC开始转换,相邻两次CNV的下降沿决定了采样周期。设计一个计数器,采用一个寄存器存放该计数器的溢出值。计数器向上计数,达到溢出值时清零计数器并重新计数。计数值在0到某个值count0之间时,FPGA驱动CNV信号生成高电平,在count0到计数值之间时FPGA驱动CNV信号生成低电平。

-

采样率设置:约定好计数器计数频率和计数器溢出值,由计数器频率除以溢出值得到采样率。受限于计数器频率以及溢出值必须为整数,采样率必须为一系列分散的值。可能需要根据设置的采样率值和计数器频率进行计算,取整后得到溢出值。

-

本文章使用limfx的vscode插件快速发布