ad采集udp发送ddr3存储

功能阐述

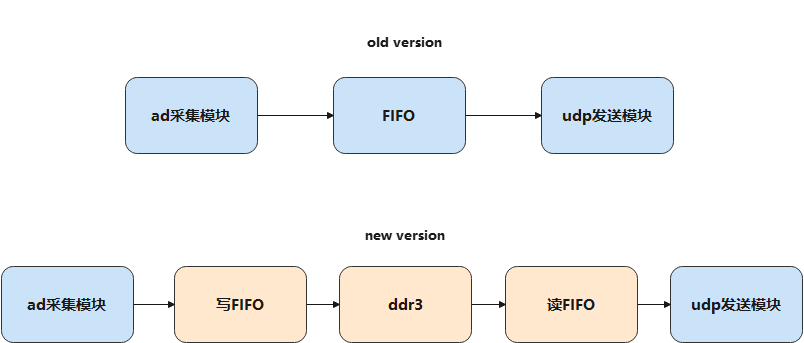

在ad采集系统中,上个版本是通过FIFO缓存ad数据然后发送到udp模块的,如下图上半部分所示

本周的工作就是将缓存数据的FIFO部分替换为ddr3存储,ad采集模块和udp发送模块保持不变,如下图所示

写FIFO和读FIFO的功能是位宽转换(16位<->128位)和缓冲

ddr3能存储数据

数据流向为ad采集后进入写FIFO,然后写入ddr3,然后立马读出进入读FIFO,然后进入udp发送模块

遇到问题

-

刚开始遇到的问题是mig功能无法正常行使,后来发现是输入时钟不正确,龙哥程序里给了个MMCME2_BASE分频出的200m时钟无法驱动mig,但使用clock wizard IP核进行时钟转换后(200m到200m,只是经过clock wizard)就可以使用mig了。这个问题可以再研究一下。

-

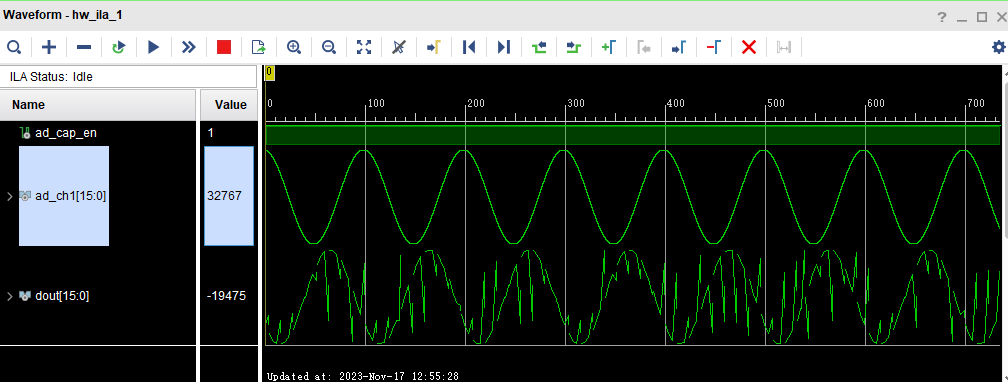

可能是存储的时序不正确,数据进出ddr3后的结果如下图所示

ad_ch1是刚采集到的数据,dout是读fifo读出的数据,发现读出的数据有明显失真现象,怀疑是读写时序的问题,还在修改中。

取巧方法

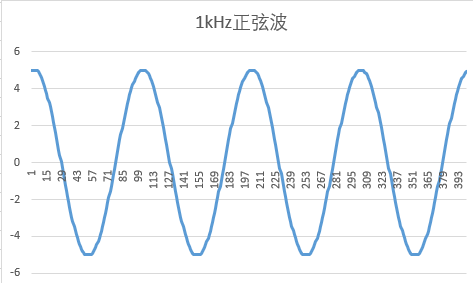

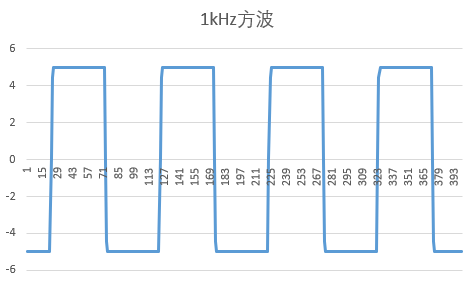

尝试去掉读写FIFO,直接将ad信号写入和读出mig,效果很好

再拿NetAssist测一下通过udp发送的包,效果也不错

分析的话应该是使用fifo读写的时钟和mig读写的时钟没有匹配好,所以波形会出现失真,单独使用mig就没这个问题

所以现在实现的是最简单的形式: ad模块->ddr3->udp模块

本文章使用limfx的vscode插件快速发布