ADC与FPGA测试

AD Card修改

-

电压测量设备从之前的4位万用表更换为 DMM4020 5位半万用表,重新进行关键电压的测量。

-

第一版中由于采用LTC2324的内部基准源,使得基准输出存在问题。第二版已更换为REF3440基准,即采用外部基准源,每个通道配备一个REF3440。

-

现有基准:输出4.0962V,精度0.005%,远超LTC2324内部基准。

-

增益修正:单个电压输入测量,差分输入电压4.8999V,差分输出电压1.5680V,计算得到增益位0.3200065,增益误差0.0002%。

ADC转换测量

-

该ADC需要输入CNV信号和CLK信号,返回SCK信号和SDOA-D数据信号。

-

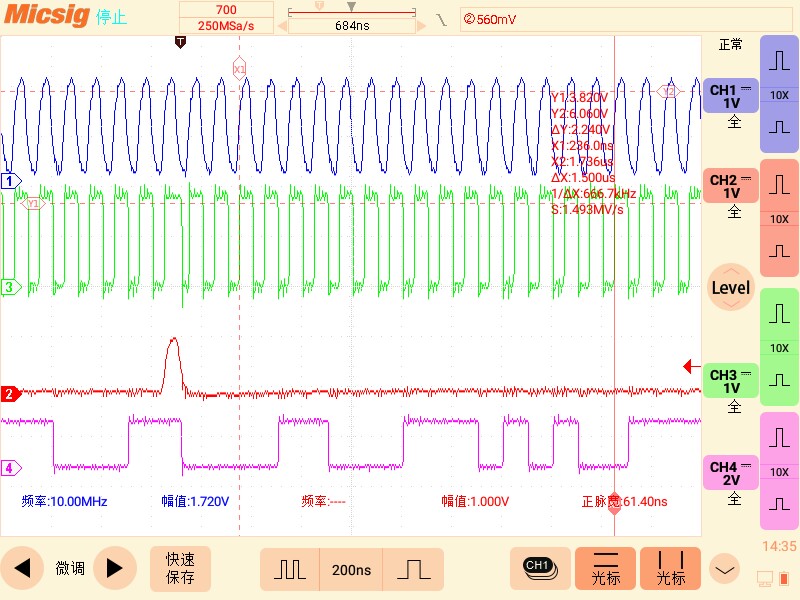

首先采用信号发生器输出满足要求的CNV信号和CLK信号,采用示波器观察SCK信号的SDOA信号,人工进行数据读取,校验ADC转换的准确性。

-

CNV信号:200kHz,50ns高电平。CLK信号:10MHz,0-1.8V高低电平。CLK信号受限于探头的带宽,无法高于10MHz,否则信号波形容易失真。

-

输入特定的4组直流电压进行测试。CNV信号下降沿开始转换,220ns后数据开始输出。设定CNV信号下降沿触发示波器采集,读取220ns后最近的一个SCK上升沿,作为数据读取的开始边沿。向后读取约15个边沿,完成16bits数据的读取。

-

5V输入下,输入电压测得4.9842V。读的数据为 0011 0001 1101 0011,转换为带符号整形,为12755。根据ADC转换的线性公式,转换电压电压为 12755*VREF/32767 = 4.9828V,误差为0.028%。

-

1.8V输入下,输入电压测得1.8078V。读的数据为 0001 0010 0001 0001,转换为带符号整形,为4625,计算得到转换电压为1.8067V,误差0.06%。

-

+6V输入下,输入电压测得6.0624V。读的数据为0011 1100 0101 1001,转换为15449,计算得到转换电压为6.035V,误差0.45%。

-

-6V输入下,输入电压测得-6.0730V。读的数据为1100 0011 1011 0101,转换为-15435,计算得到转换电压为-6.029V,误差0.72%。

-

-

到此完成ADC初步测试,可认为测量准确,下一步结合FPGA进行数据读取测试。

FPGA控制ADC转换与数据读取测试

-

FPGA代码总体设计:基于状态机和采样控制计数器。

-

采样控制计数器:采用100MHz时钟驱动,向上计数。计数上限为:(100MHz/sample rate)- 1,该计数器直接决定采样率。

-

状态机:分为6个状态。每个状态的转换由采样计数器的计数值达到一定阈值后触发转换,完成各个状态持续时间的控制。

-

idle状态:空闲,不做任何事。

-

conv状态:生成CNV转换脉冲,持续30ns。

-

busy状态:等待ADC转换完成,持续230ns。

-

read状态:生成CLK时钟,并进行数据读取。CLK时钟具备16个脉冲。持续160ns。

-

rdend状态:读取完成状态,用于匹配数据读取时钟SCK和主时钟间的延时。持续20ns。

-

latch状态:锁存数据读取寄存器的值,用于写FIFO。持续10ns。

-

-

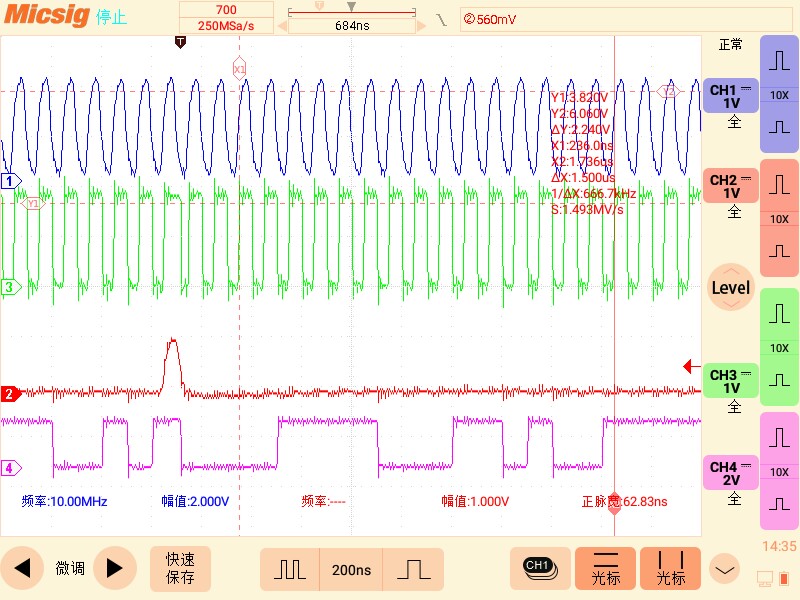

测试结果:仿真通过。实际上板测试出现bug,具体如下:

-

硬件上:代码需要SCK信号作为数据读取的时钟,SCK信号引脚不能随意连接,需要连接到FPGA上专用的时钟引脚上。设计的底板上SCK对应信号引脚不具备时钟输入功能,需要飞线到其他引脚上才能完成时钟输入。

-

实际上SCK信号不完全是CLK信号的复制,还包括了转换脉冲。如下,在16个脉冲信号后还包括一个较大的脉冲,该脉冲为CNV信号。采用如下的SCK信号作为读取时钟时,会在CNV脉冲的上升沿触发一次数据读取和移位,导致数据出错。

-

后续需要对数据读取部分进行修改。官方给出的方案是采用状态机,将所有bits的读取都分解为状态机,16bits读取则需要16个状态,每读取一个bits就跳转到下一个状态。可以自行编写,也可以基于官方的代码进行修改。

-

本文章使用limfx的vscode插件快速发布