ADC精度测试与数据读取模块设计

ADC FPGA读取代码

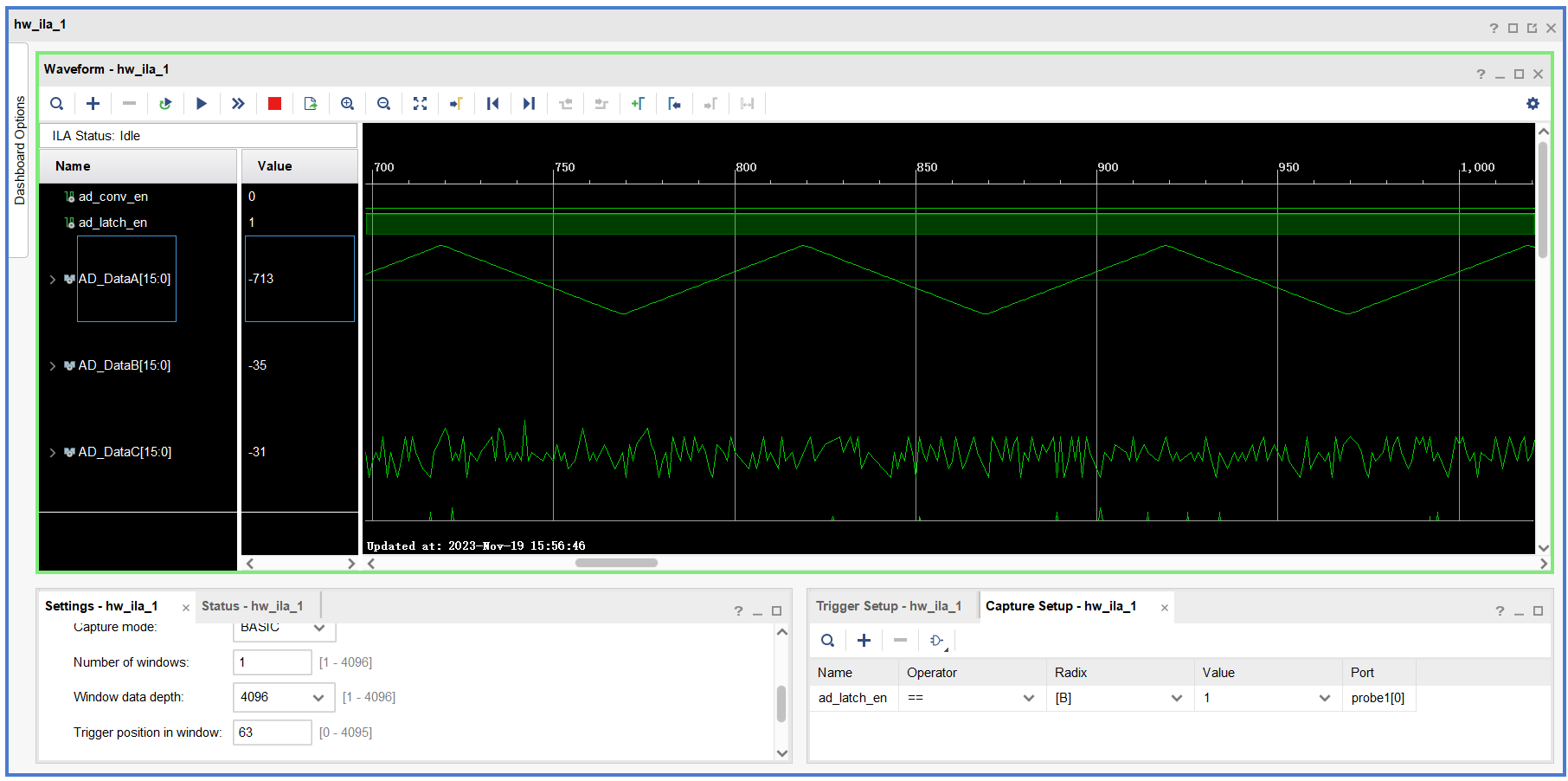

参考ADI官方例程,将DCO回波时钟驱动的16bits数据读取代码修改为状态机读取,可以实现数据读取与波形重建。采用ILA进行数据的传输,效果如下。

ADC与AFE交直流分析

主要进行两类分析:直流分析与交流分析。

-

直流分析:对AFE与ADC输入特定值的直流电压值,根据输出数据和输入电压得到整个测量的直流传递函数,得到直流测量的精度。

-

交流分析:对AFE与ADC输入特定值、特定频率的交流电压信号,利用直流分析得到的传递函数进行交流分析,得到交流测量的精度。

-

其余分析:INL、DNL、SFDR等等。

-

INL:积分非线性,反映ADC实际传递函数与理想传递函数间的误差。理想ADC的INL为0,实际不为0。

-

DNL:微分非线性,反映ADC实际传递函数的单调性与斜率变化。ADC的DNL应该越近0越好,表明ADC传输函数越线性,不存在某个数据点处的斜率突变。

-

SFDR:无杂散动态范围,反映了FFT分析频谱中信号幅值与最大谐波的距离关系。所以SFDR值越大则说明系统的噪声水平越低,ADC的动态性能越好。

-

SNR:信号与噪声的比值。理想ADC满足:SNR = 6.02*N + 1.76dB,N为ADC分辨率。

-

THD:总谐波失真,输入信号与系统所有谐波的总功率比。

-

SINAD:信纳比,信号+噪声+谐波的功率与谐波+噪声的功率比值。SINAD很好地反映了ADC的整体动态性能。

-

-

分析时采用以下设备:

-

万用表:DMM4020 5位半台式万用表,自动量程,慢测量速度。

-

信号源:泰克AFG3022C,双通道,250MSa,1uHz分辨率。

-

示波器:麦科信STO10004,四通道,1GSa,8bits分辨率。

-

直流源:WANPTEK 30V@10A

-

直流分析

输入电压产生和测量方法

输入电压采用AFG3022C产生,采用DMM4020监视输入电压,数据分析基于vivado、csv和matlab进行。具体操作方法如下:

-

设定工作模式为双通道、两路反相输出,频率和电平相等。CH1接入AIN+,CH2接入AIN-。

-

输出波形为方波,频率1mHz,周期1000s,单次测量具有500s稳定电平时间。

-

输出阻抗设定高阻抗,则输出电平与设定值基本一致。选择50Ω则输出电平为设定的2倍。

-

输出电平可调,高电平

0 ~ 6V,低电平-6V ~ 0V,总的差分电压输入范围为-12V ~ 12V。 -

单次调节同时调节高电平和低电平各

0.1V,总差分输入电压变化0.2V。 -

单次测量时,同时读取DMM4020测量值,并在vivado上采用ILA进行采样,完成一次测量。

-

ADC测量数据导出到csv文件,在matlab上进行分析。

输入-输出曲线拟合方法

曲线拟合采用Matlab cftool和polyfit函数。cftool用于直观显示用何种拟合方式以及显示SSE、R2等拟合优度参数。polyfit用于得到更加精确的拟合系数值。

-

采用

readtable函数读取ADC1_Ch1_DC_Test_New.xlsx文件,文件第1行为输入电压值,对应第2行为各个输入电压值下的4096个采样数据点的平均值,第3-4098行为实际测量值。 -

实际使用时仅需要使用第1、2行数据进行拟合,3-4098行数据可以用于直流测量下的噪声分析。为保证线性,仅采用

-11V ~ 11V输入下的数据进行拟合。 -

采用

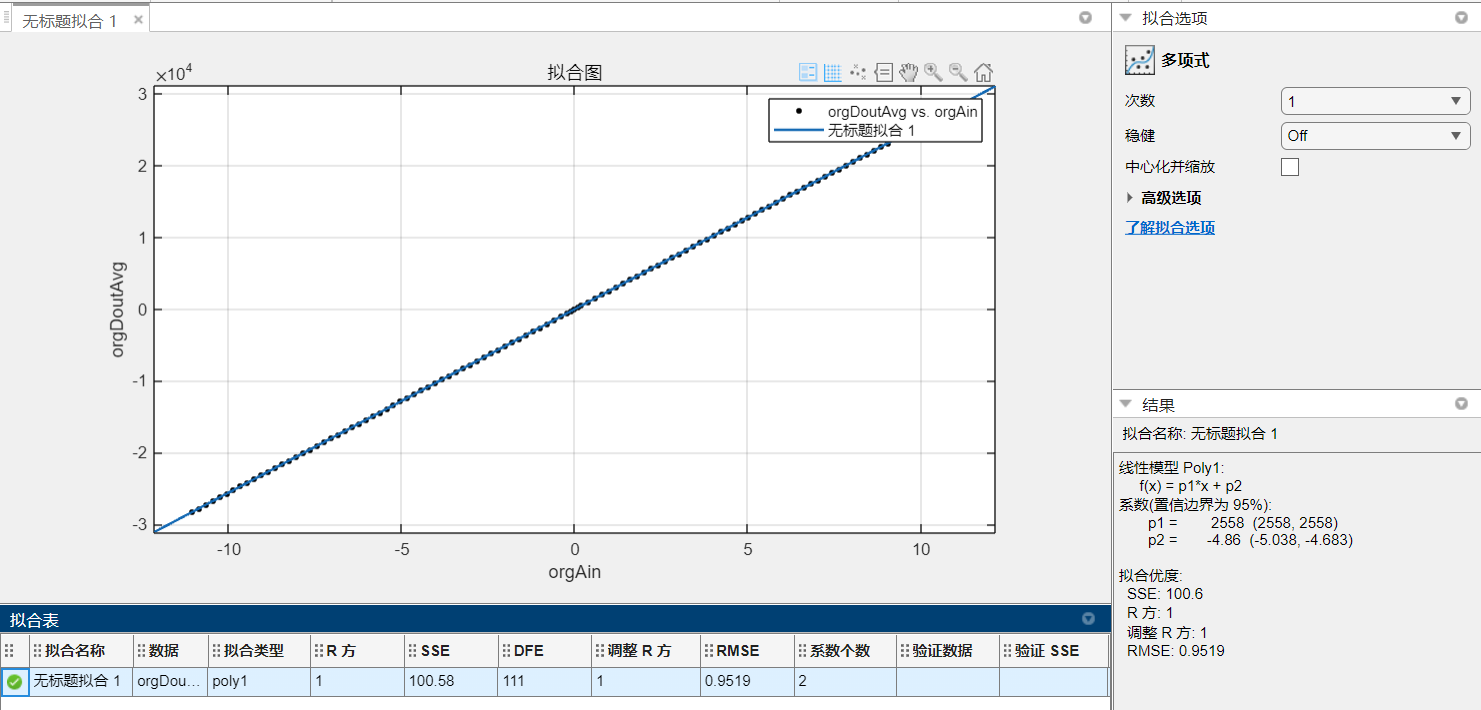

cftool进行拟合,x轴数据为orgAin即原始输入电压,y轴数据为orgDoutAvg即原始测量数据平均值。拟合采用一次多项式拟合,R方和调整R2均为1,线性度很好。

-

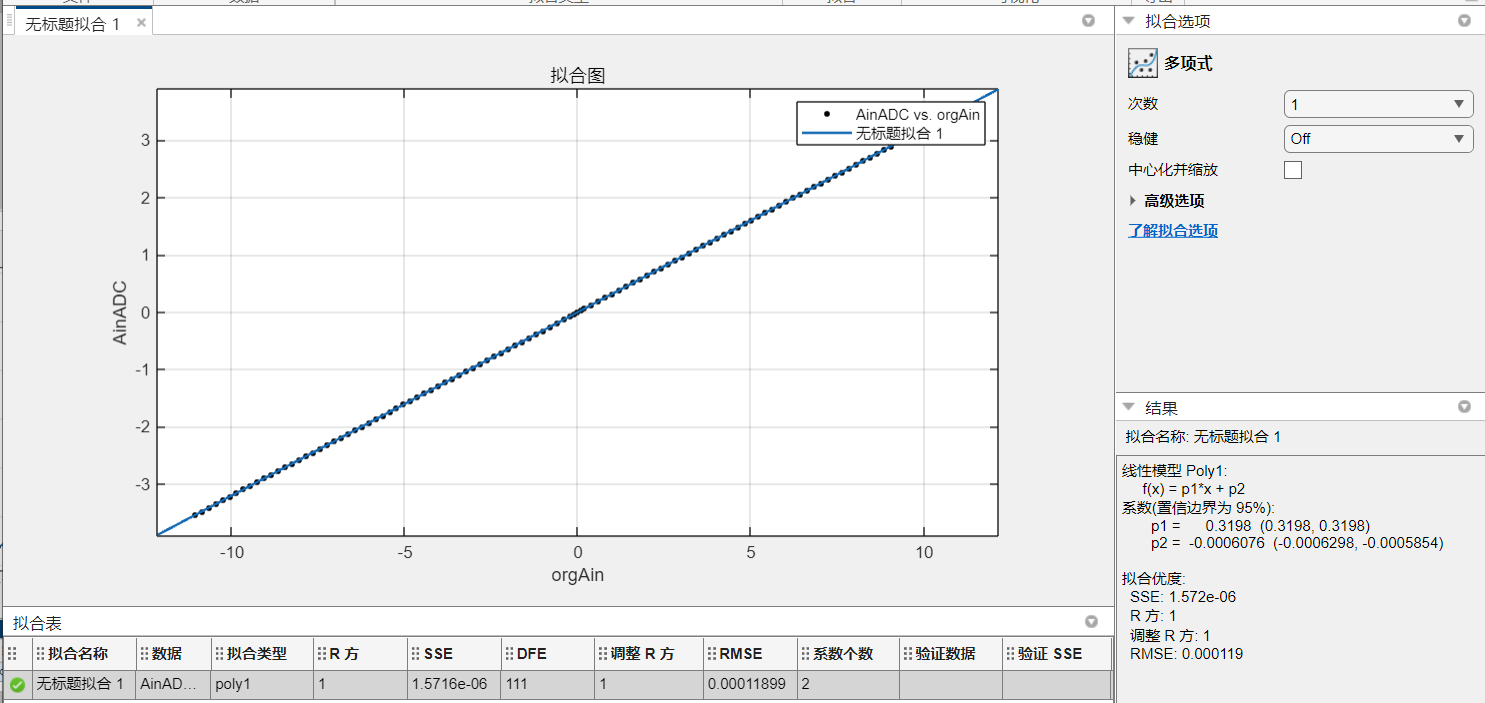

直接对输入电压和输出数据进行拟合后发现SSE和RMSE都偏大,主要原因是原始数据输出数据项远大于输入数据项。采用理想ADC转换公式将ADC输出数据换算到ADC输入电压,即AinADC,再次拟合。得到斜率为

0.3198,截距-0.0006076。以上斜率反应AFE性能,AFE的增益即为0.3198,增益误差0.063%。该拟合下SSE和RMSE均很小。

-

确定采用一次函数进行拟合后,采用

polyfit函数进行拟合,x轴为orgAin,y轴为orgDoutAvg。得到更精确的系数如下:斜率为2558.1266,截距为-4.8065。

输入-输出曲线校核方法

输入电压-输出数据曲线采用特定直流输入进行校核,可用于分析直流测量精度。

-

输入特定电压,以上电压不等于传递函数测试输入电压。

-

输出数据平均值通过传递函数计算拟合后的电压值,同时读取DMM4020测量电压作为输入电压,计算二者的相对误差。

-

测试结果见下表,相对误差基本在

±0.01%左右,较为准确。

| 输入电压(V) | 输出数据平均值 | 输入电压拟合值 | 相对误差(%) |

|---|---|---|---|

| 10.0953 | 25819.5125 | 10.0950 | 0.00297168 |

| 7.5834 | 19394.1049 | 7.5833 | 0.00131867 |

| 5.0696 | 12965.2387 | 5.0702 | -0.011835253 |

| 2.5558 | 6533.3663 | 2.5559 | -0.003912669 |

| -2.5544 | -6540.0252 | -2.5547 | -0.011744441 |

| -5.0676 | -12969.5294 | -5.0680 | -0.007893283 |

| -7.5812 | -19397.4133 | -7.5808 | 0.00527621 |

| -10.0921 | -25820.0456 | -10.0914 | 0.006936118 |

直流测量噪声分析

直流测量包含一定的噪声。

-

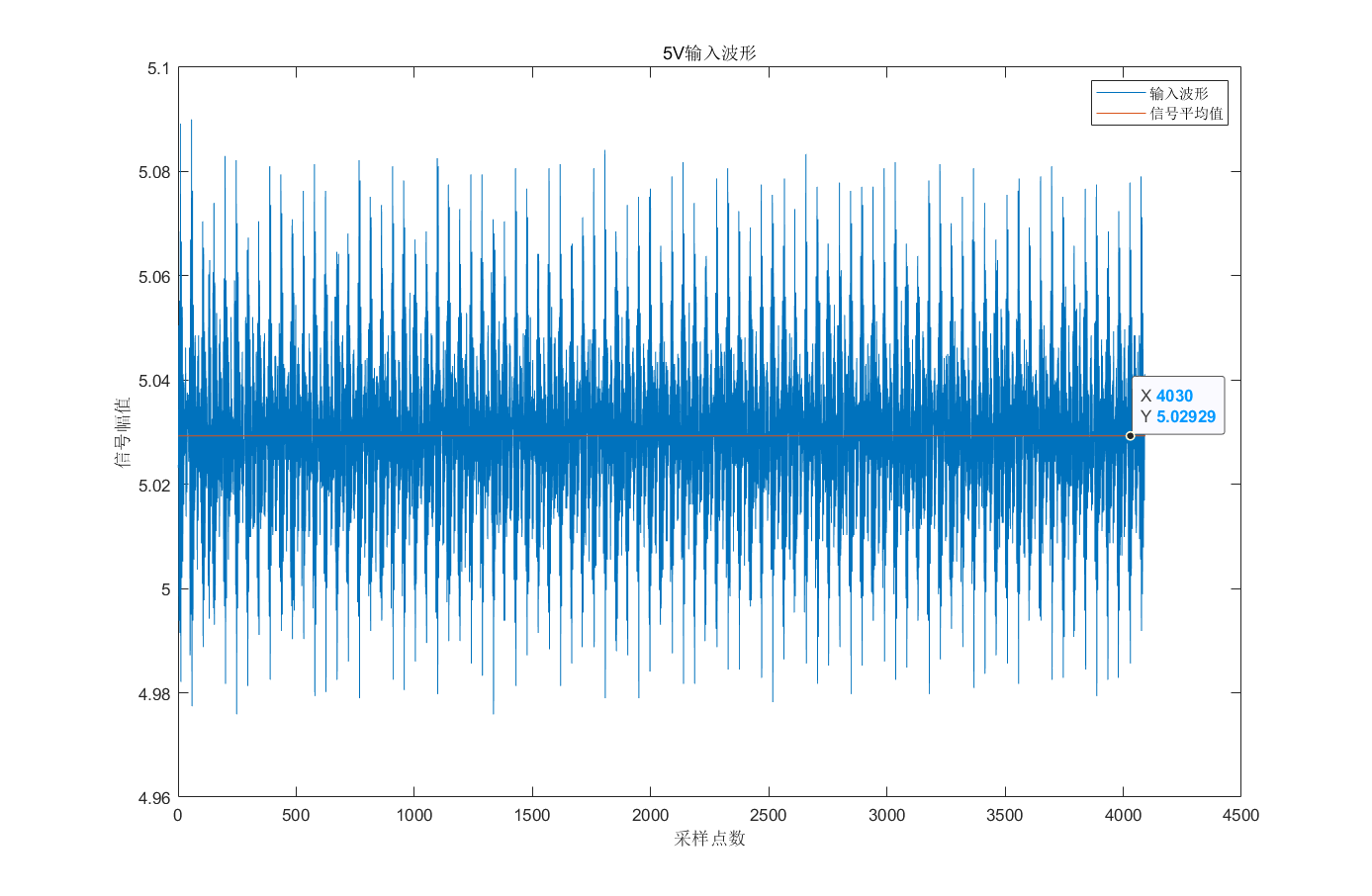

以

5V输入为例,将原始4096个采样点换算到实际输入电压,波形如下,包含一定的噪声,并且在频率上呈现一定的周期性分布。5V输入下平均值为5.02929V,DMM4020测得为5.0290V,相对误差-0.0057%,仍然准确,说明噪声不影响输入电压的测量,是一个周期性信号。

-

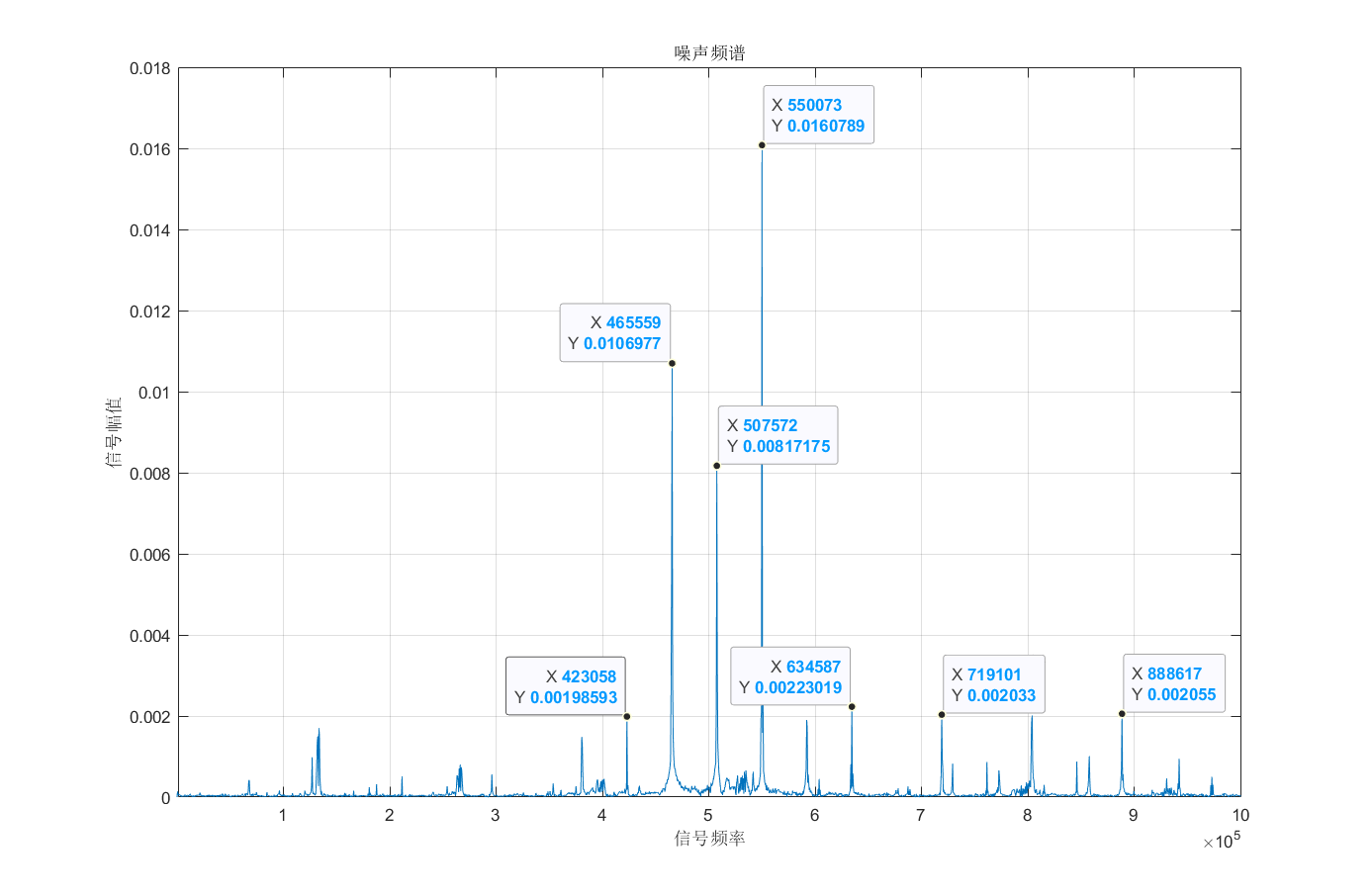

采用FFT函数对4096个采样点对噪声做DFT分析,噪声数据由原始数据减去平均值得到。噪声频谱如下,主要由三个峰,对应频率为

550.073kHz、465.559kHz、507.572kHz,均在8mV ~ 16mV之间。考虑到ADC和AFE供电、FPGA板卡供电等等均包含了开关电源,百kHz又是开关电源常见的开关频率,以上尖峰可能由各个供电电源接地不良好导致、电源噪声相互干扰导致。

-

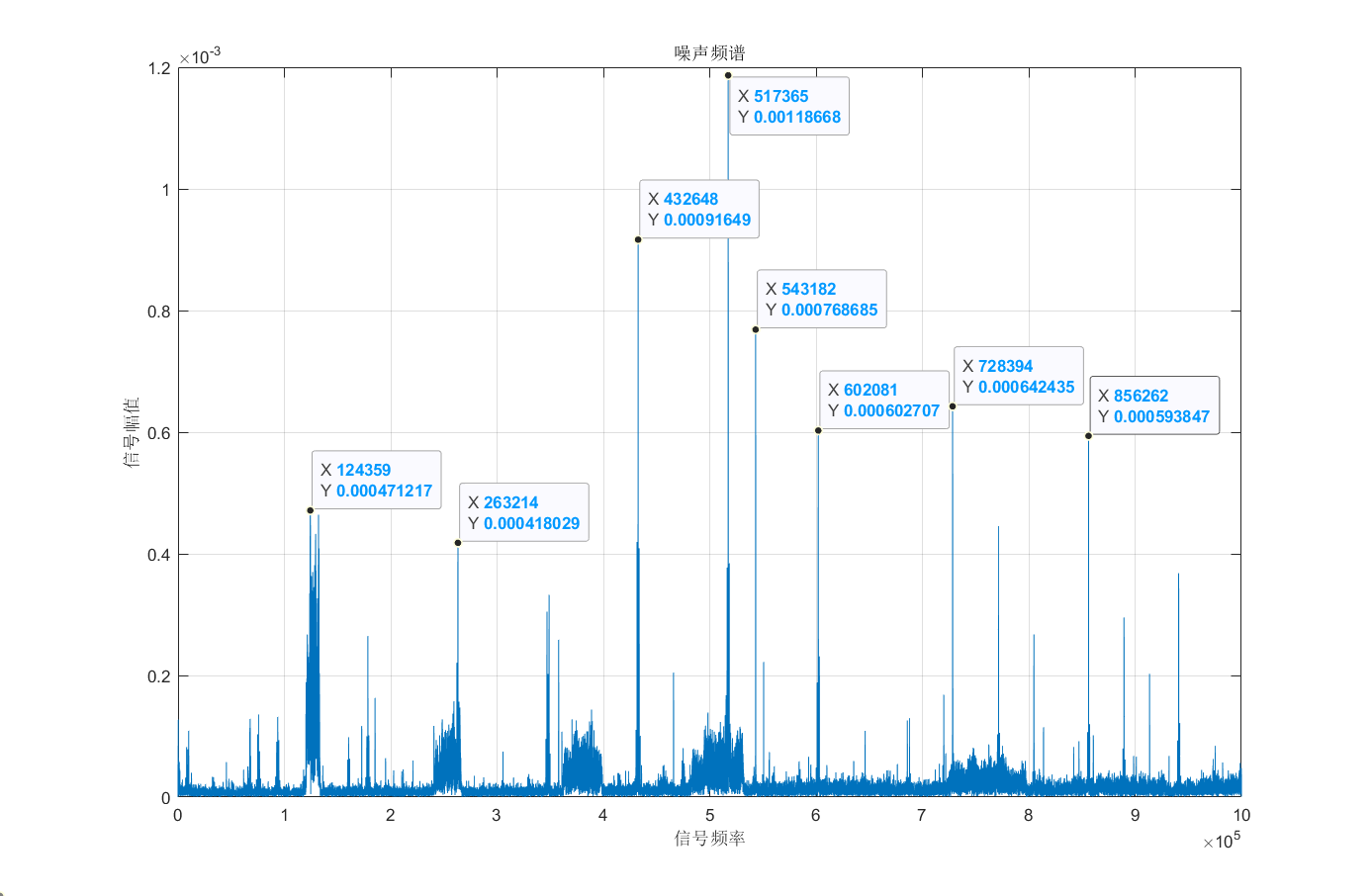

后续做直流曲线校核时,对FPGA板卡的主输入电源,即

WANPTEK开关电源做了接地处理,将VO_0V端子和GND端子相连。重新对其中一个电压输入点5.0696V做噪声频谱分析,结果如下。仍然存在多个峰,频率与上图接近,但幅值都降低到1mv左右。

-

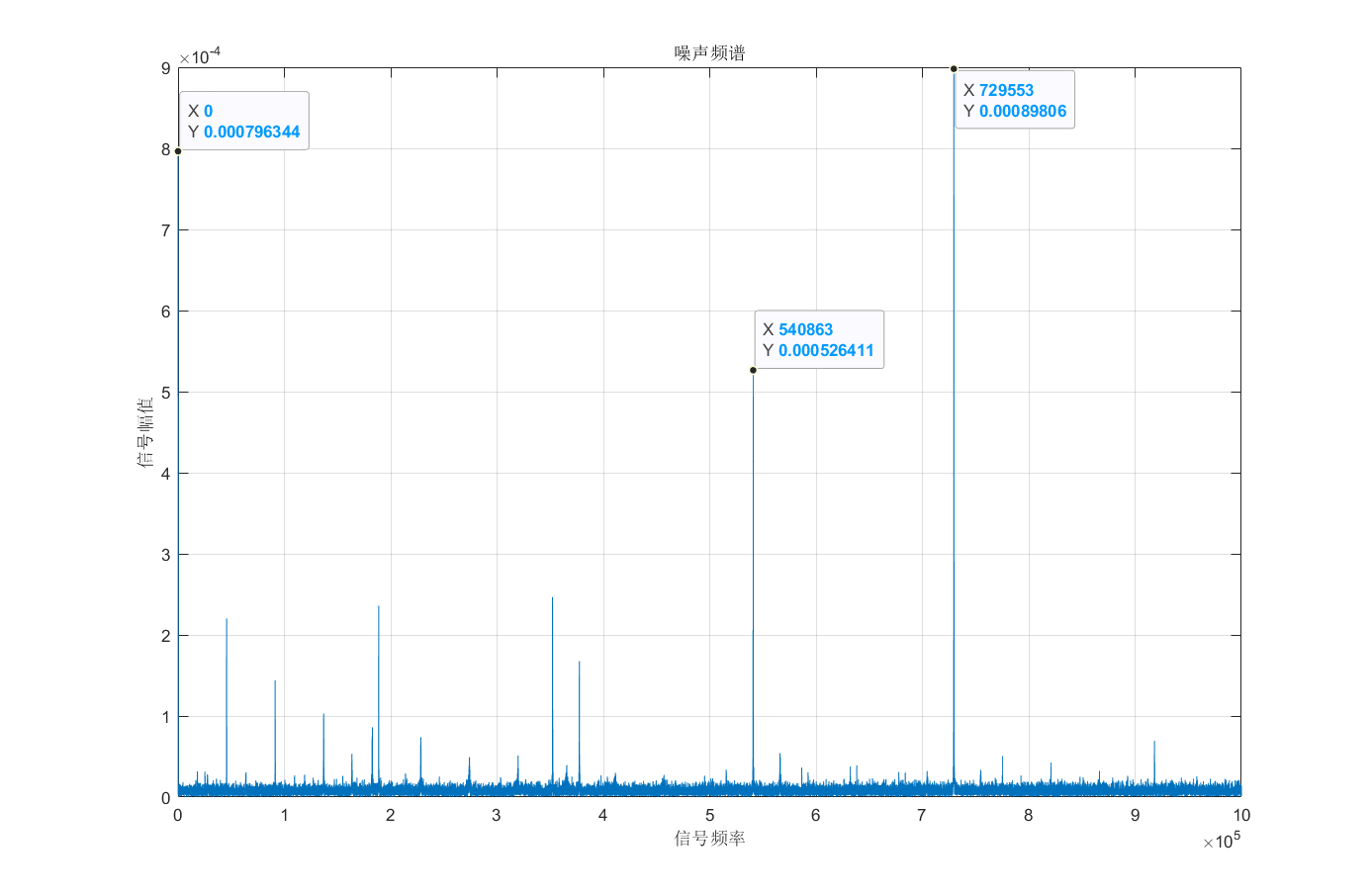

另外分析了

0mV输入下的噪声,即AIN+、AIN-均接入GND。噪声频谱如下,包含直流峰值、540.863kHz、729.553kHz三个峰。直流峰值约0.796mV,可以认为是AFE的固定直流偏置。后两个峰值中,540kHz可能还是由于开关电源的干扰,729kHz峰值不明确。3个峰的峰值都在1mV一下,对应约6LSB,除非做mV级别测量,否则不影响测量。

交流分析

输入电压产生和测量方法

交流输入电压产生方法和测量方法与直流测量一致,不同在于:

- 将直流测量中的

1mHz的方波替换成频率可调的正弦波; - 固定双通道正弦的幅值为5V,则输入差分电压的幅值为10V,峰峰值为20V,达到设计的满量程。

交流测量精度

-

交流测量下,曲线采用直流测量下拟合出的输入-输出曲线,单次测试包含约65536个测试数据。

-

采用matlab读取测试数据文件中包含的全部完整的正弦周期数据,统计以上数据的

RMS,与DMM4020的交流档测试出的有效值比较,计算得到相对误差。结果如下表所示。

| 输入频率(Hz) | 输入电压RMS(V) | 输入电压RMS拟合值 | 相对误差(%) |

|---|---|---|---|

| 70 | 7.1397 | 7.157 | -0.2423071 |

| 100 | 7.1394 | 7.1573 | -0.250721349 |

| 500 | 7.1325 | 7.1506 | -0.253767964 |

| 1,000 | 7.1289 | 7.1472 | -0.256701595 |

| 5,000 | 7.1277 | 7.1454 | -0.24832695 |

| 10,000 | 7.1292 | 7.1456 | -0.230039836 |

| 50,000 | 7.1292 | 7.109 | 0.283341749 |

| 特殊频率 | |||

| 122.0703125 | 7.1376 | 7.1557 | -0.25358664 |

| 488.28125 | 7.132 | 7.1501 | -0.253785754 |

| 976.5625 | 7.1286 | 7.1468 | -0.255309598 |

| 1,953.125 | 7.127 | 7.145 | -0.252560685 |

| 4,882.8125 | 7.1268 | 7.1445 | -0.248358309 |

| 9,765.625 | 7.1284 | 7.145 | -0.232871332 |

| 19,531.25 | 7.1293 | 7.1417 | -0.173930119 |

| 48,828.125 | 7.1246 | 7.1109 | 0.192291497 |

| 97,656.25 | 7.0981 | 7.0125 | 1.205956524 |

| 195,312.5 | 6.9799 | 6.6869 | 4.197767876 |

- 在

70Hz ~ 50kHz频率带内相对误差在0.25%以内,在高于100kHz后测量误差逐渐增大,在200kHz测量误差约4.2%,主要因为设计时AFE的带宽约为560kHz,200kHz已经接近-3dB点,增益有所下降。交流测量的精度较直流测量的精度有所下降。

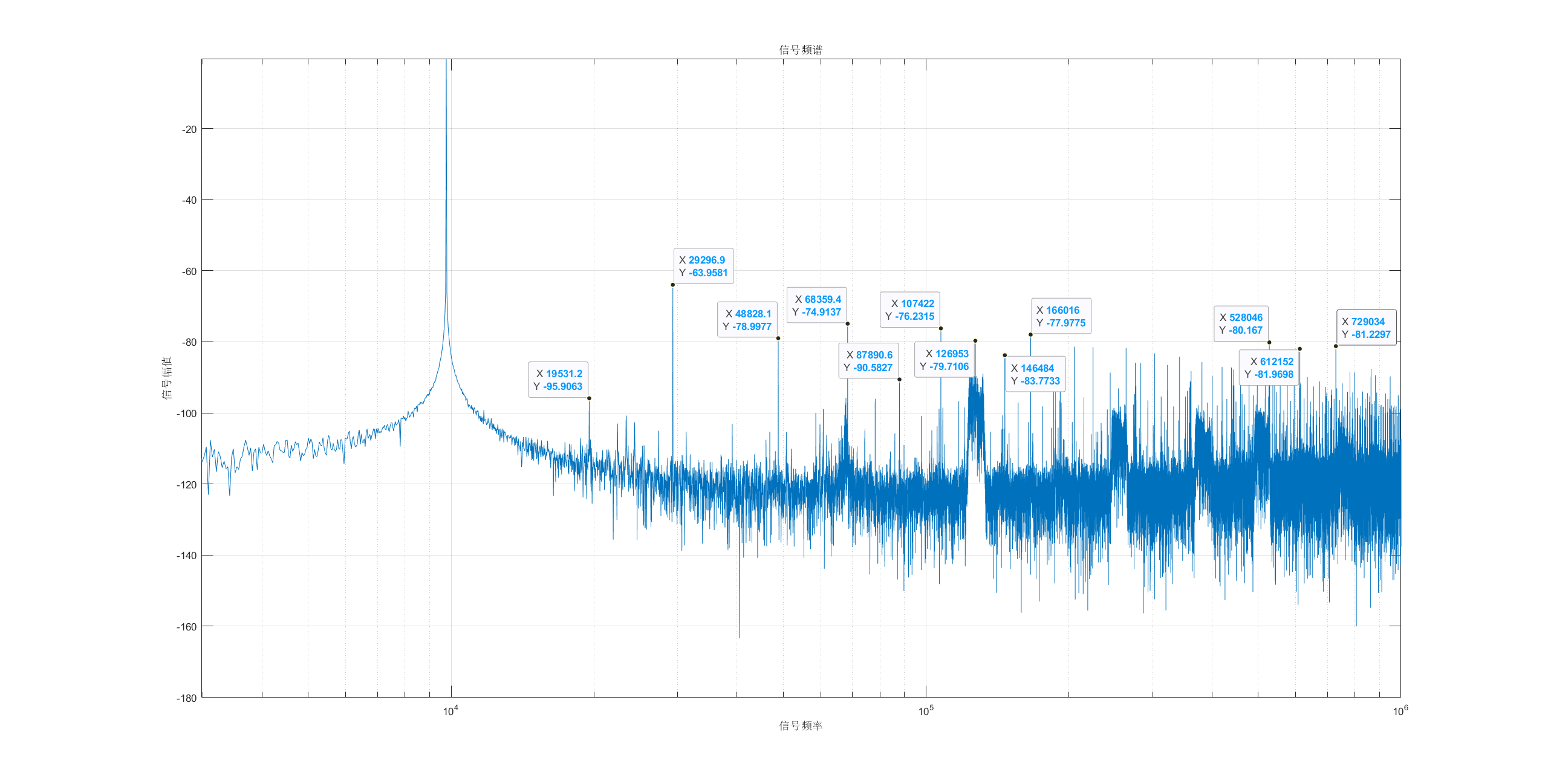

交流测量频谱分析

交流测量数据除了包含输入信号的基波频率外,还包含其他信息。分析交流测量输出数据频谱可以分析整个测量的动态范围、噪声分布等信息。

-

对以上数据可以进行FFT分析。取特殊频率的原因在于,ADC使用2M采样率,在65536个采样点下可以使得正弦波具有整数个周期,不浪费任何一个数据点。

-

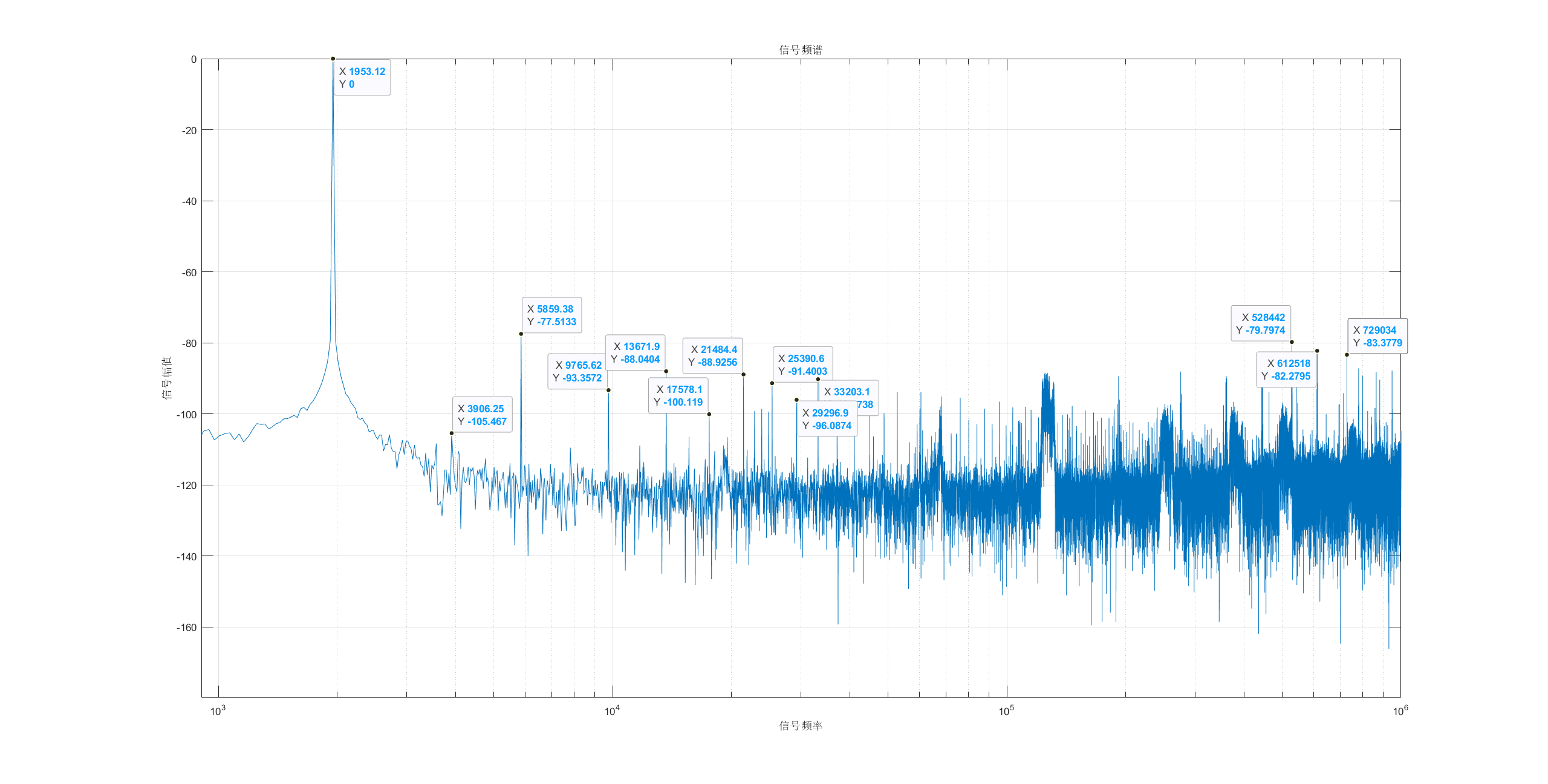

取

1953.125Hz作为分析频点,接近2kHz。取1953.125Hz下的输入信号频率幅值为单位1,绘制整个频谱。主峰为输入信号频率点1953.125Hz,余下为基波信号的3 ~ 17次谐波,且均为奇次谐波。

-

取

4882.8125HzV为分析频点,接近5kHz。显示3 ~ 17次谐波,均为奇次谐波。显示一个9765.625Hz的偶次谐波,但是幅值很小。

-

取

9765.625Hz为分析频点,接近10kHz。仍然显示出3 ~ 17次谐波,且同样为奇次谐波。此外还显示一个19531.2Hz的偶次谐波,但是幅值很小。

-

若认为ADC采样数据的噪声主要来源于

基波频率外的频带,则3次谐波为主要的噪声源。且随着信号频率的上升,三次谐波的含量越来越高。第2、3个谐波来源则为7次和11次谐波,但都低于3次谐波约10dB左右。 -

以上频谱除了输入信号的基波频率和各次谐波外,统一发现三个与奇次谐波幅值接近的峰,分别为

528kHz、612kHz、729kHz。除了528kHz可能由ADC与AFE的开关电源供电产生外,其余两个频点不详。以上三个频点都在-80dB左右,对数据测量影响不大。

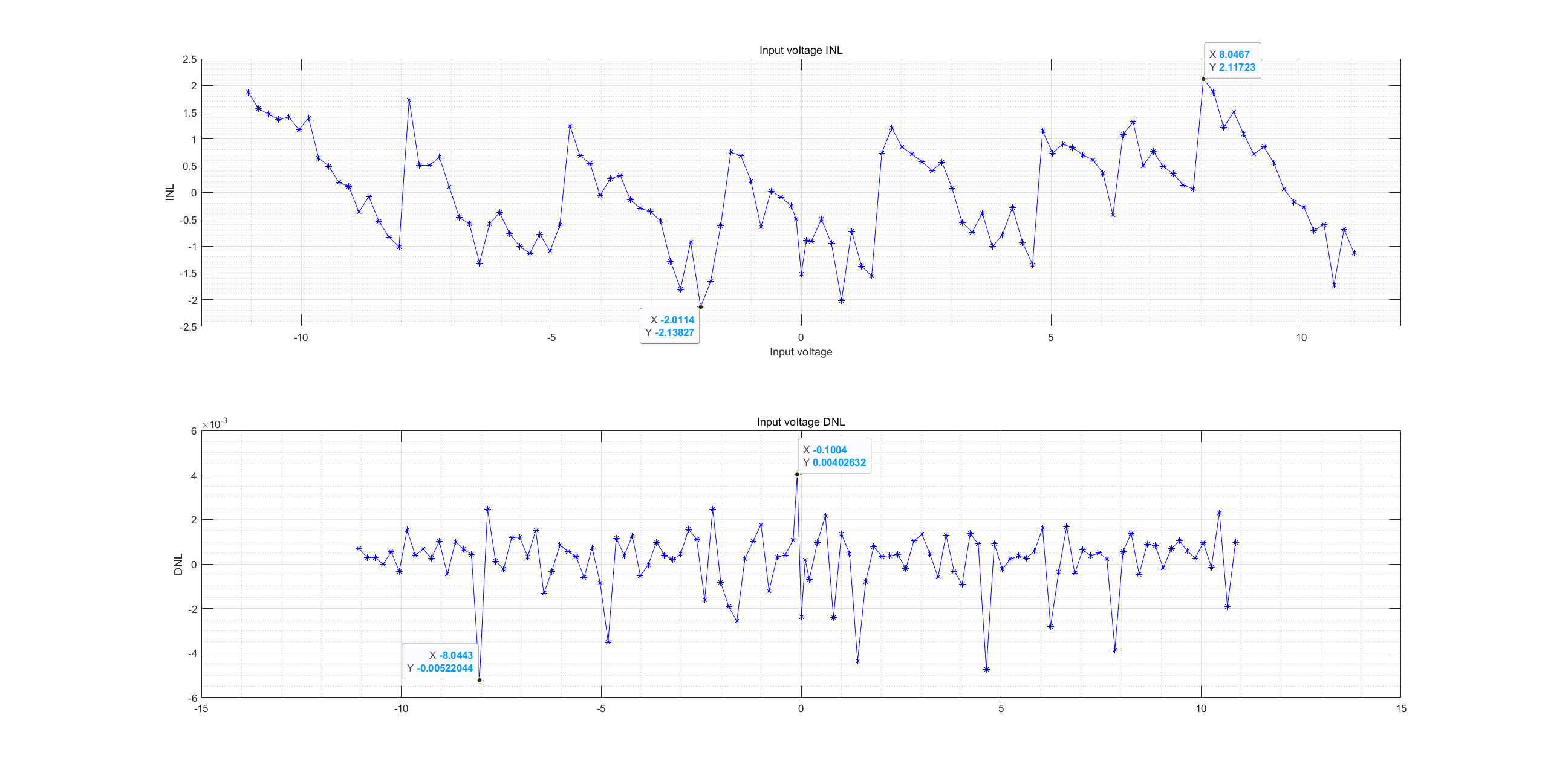

其他分析

-

INL和DNL分析如下,可以与直流分析一并测量。主要反映板载ADC的性能。

- 测试出INL在

-2.13 ~ 2.11之间,可以认为测试数据中,误差主要集中在5 ~ 6个LSB之间,其余数据测量准确。通过INL,得到ADC的测量精度为0.0092%。对比LTC234的数据手册,INL典型值为±2LSB,基本达到数据手册要求。 - 测试出DNL在

-0.005 ~ 0.004之间,可以认为ADC的线性度很好,没有出现斜率的变化。LTC2324数据手册中DNL的典型值为±0.4LSB,基本达到要求。另外由于本次测试数据点稀疏,需要更加精确的DNL需要进行缩小输入电压进行测试。

- 测试出INL在

- SFDR分析需要结合交流测量的频谱。定义ADC输出数据的谐波为除了输入信号基波分量外的所有频率分量,则SFDR为基波分量与三次谐波分量的幅值差。频谱幅值相较于基波分量幅值进行归一化,分析结果见下表。可见随着输入信号频率的增大,SFDR逐渐减小。由于交流测试缺少标准仪器如高速示波器,仅作参考。

| 输入频率(Hz) | 三次谐波幅值(dB) | 最大幅值谐波频率 | SFDR(dB) |

|---|---|---|---|

| 122.0703125 | -89.3247 | 528900 | 80.1322 |

| 488.28125 | -89.9781 | 528625 | 78.7802 |

| 976.5625 | -83.714 | 528473 | 80.7132 |

| 1,953.125 | -77.5133 | 5859.33 | 77.5133 |

| 4,882.8125 | -69.7356 | 14648.4 | 69.7356 |

| 9,765.625 | -63.9581 | 29296.9 | 63.9581 |

| 19,531.25 | -58.2971 | 58593.8 | 58.2971 |

| 48,828.125 | -51.1614 | 146484 | 51.1614 |

| 97,656.25 | -47.3468 | 292969 | 47.3468 |

| 195,312.5 | -45.8114 | 585938 | 45.8114 |

数据处理模块设计

-

基于FIFO实现,放置于ADC数据输出后。

-

FIFO需要确定最大深度,暂定为128。FIFO输入宽度为

4*16bits,即一个ADC的所有输出数据。输出同样为4*16bits,后续做拆分。 -

该模块具备3个设置寄存器,分为:

-

抽取比寄存器A:设置多少个数抽取一个数据。

-

抽取位置寄存器B:设置抽取哪一个位置的数据。

-

工作模式寄存器C:设置工作模式,暂定支持抽取或平均。

-

-

具体的抽取或平均模式放置在FIFO之后,采用读取计数器实现。

-

抽取模式下,对读取数据进行计数,每抽取比寄存器计数一轮,当达到抽取位置时,输出抽取的数据。

-

平均模式下,对读取数据进行累加,总共累加抽取比一次,当计数结束时,除以抽取比,得到输出数据。

-

-

FIFO设置工作在乒乓模式,一路写满后输出数据,交由另一路缓存数据。

-

为简化设计,数据处理模块的驱动时钟保持与ADC模块的驱动时钟一致,两者处于同一时钟域下。

本文章使用limfx的vscode插件快速发布