Zynq学习笔记

什么是Zynq

Zynq是由Xilinx,在2011年末发布的具有崭新架构的芯片。

Zynq = ARM + FPGA

在Zynq中起到核心控制和管理地位的,其实是ARM核芯片,而FPGA可以看作是ARM芯片的外围器件。

迄今为止,Xilinx公司已经发布了两种不同类型的Zynq芯片,分别是Zynq-7000 AP SoC和Zynq UltraScale+ MPSoC。

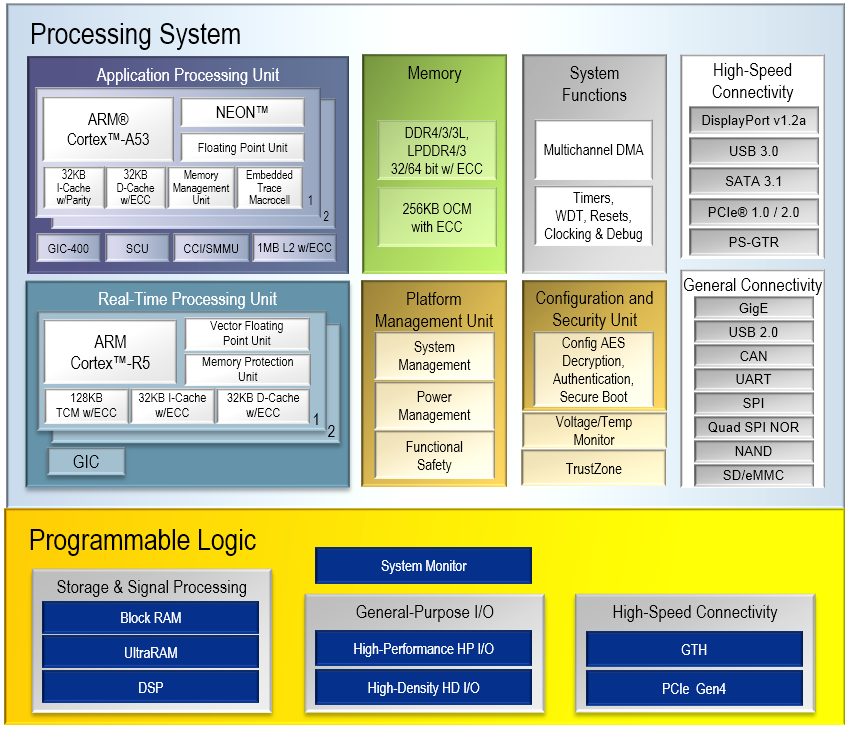

后者是前者的进化版,Zynq-7000 AP SoC的处理器内核是双核ARM Cortex A9,而Zynq UltraScale+ MPSoC的内核变成了四核的ARM Cortex A53,而且额外增加了GPU,视频编解码器等,外设资源也更丰富了。

Zynq结构框图

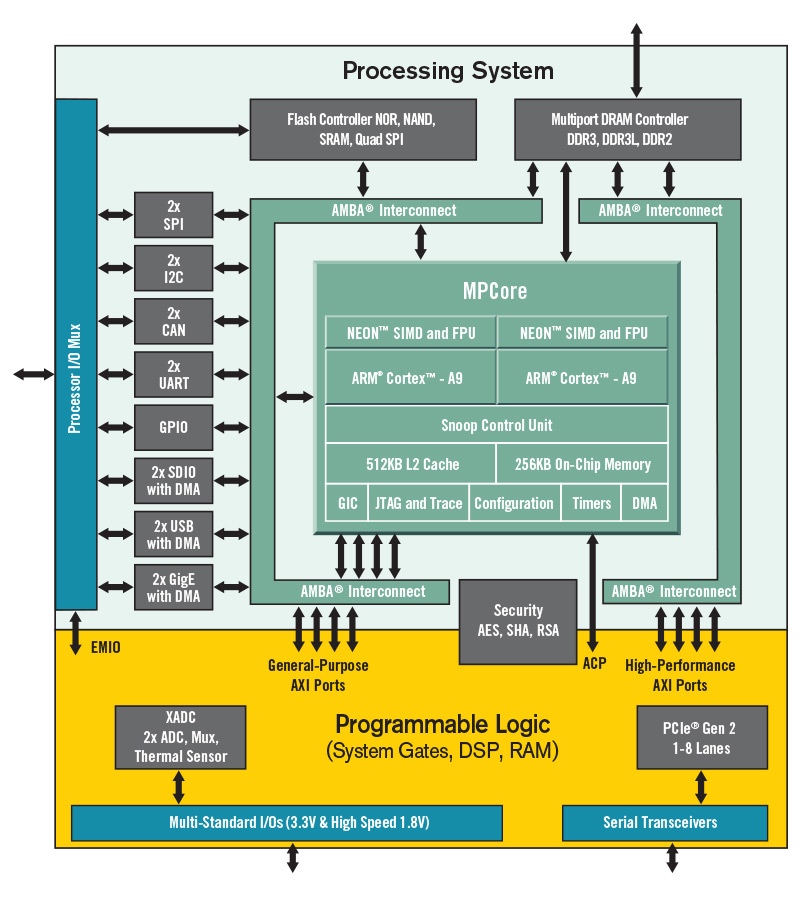

Zynq-7000 SoC

Zynq 7000 系列包括单核 Zynq7000S 器件和双核 Zynq-7000 器件,是具有出色单位功耗性价比的全面可扩展的 SoC 平台

Zynq UltraScale+MPSoC

Zynq™ UltraScale+™ MPSoC 器件不仅提供 64 位处理器可扩展性,同时还将实时控制与软硬件引擎相结合,支持图形、视频、波形与数据包处理。置于包含通用实时处理器和可编程逻辑的平台上,三个不同变体包括双核应用处理器 (CG) 器件、四核应用处理器和 GPU (EG) 器件、以及视频编解码器 (EV) 器件, 为 5G 无线、下一代 ADAS 和工业物联网创造了无限可能性。

在Zynq开发中,习惯性将处理器内核部分称为PS(Processing System),FPGA部分称为PL(Programmable Logic)。

PS部分,从图中可以看出,除了双核ARM外,还包括SPI、I2C、CAN、UART、USB等常用总线接口,千兆以太网接口,NOR Flash、NAND Flash、QSPI Flash等存储介质,以及DDR2、DDR3等内存芯片。

而PL部分,由可编程逻辑,XADC,PCIE等构成。PS与PL之间由ARM提出的ABMA Interconnect互连模块进行来连接,也就是常用的AXI总线。

PS与PL间的信息交互

Xilinx 在 IP 核中继续使用 AXI 协议。AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。AXI 协议是一种高性能、高带宽、低延迟的片内总线,具有如下特点:

1、总线的地址/控制和数据通道是分离的; 2、支持不对齐的数据传输; 3、支持突发传输,突发传输过程中只需要首地址; 4、具有分离的读/写数据通道; 5、支持显著传输访问和乱序访问; 6、更加容易进行时序收敛。

在数字电路中只能传输二进制数 0 和 1,因此可能需要一组信号才能高效地传输信息,这一组信号就组成了接口。AXI4 协议支持以下三种类型的接口:

1、AXI4:高性能存储映射接口。 2、AXI4-Lite:简化版的 AXI4 接口,用于较少数据量的存储映射通信。 3、AXI4-Stream:用于高速数据流传输,非存储映射接口。

存储映射(Meamory Map)

如果一个协议是存储映射的,那么主机所发出的会话(无论读或写)就会标明一个地址。这个地址对应于系统存储空间中的一个地址,表明是针对该存储空间的读写操作。

AXI4 协议支持突发传输,主要用于处理器访问存储器等需要指定地址的高速数据传输场景。AXI-Lite为外设提供单个数据传输,主要用于访问一些低速外设中的寄存器。而 AXI-Stream 接口则像 FIFO 一样,数据传输时不需要地址,在主从设备之间直接连续读写数据,主要用于如视频、高速AD、PCIe、DMA 接口等需要高速数据传输的场合。

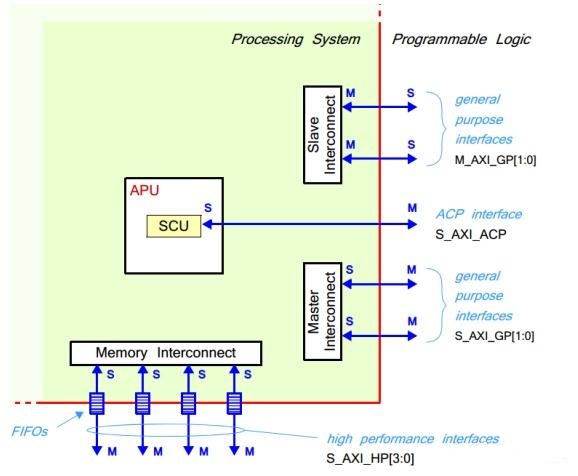

在 PS 和 PL 之间的主要连接是通过一组9个AXI 接口,每个接口有多个通道组成。这些形成了 PS 内部的互联以及与 PL 的连接,如下图所示:

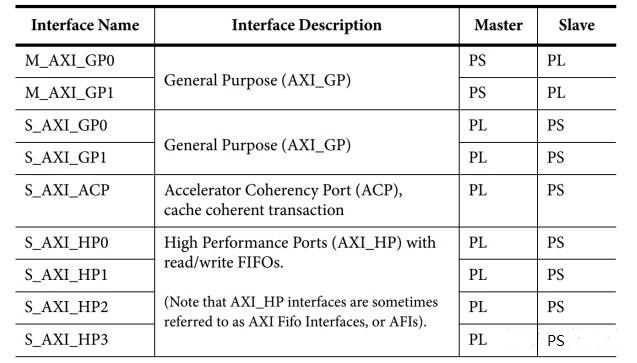

将上图中的接口总结如下所示

接口命名的第一个字母表示的是 PS 的角色,也就是说,第一个字母“M”表示 PS 是主机,而第一个字母“S”表示 PS 是从机。

PS 和 PL 之间的 9 个 AXI 接口可以分成三种类型:

1、通用 AXI(General Purpose AXI):一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是不带缓冲的透传。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。 2、加速器一致性端口(Accelerator Coherency Port):在 PL 和 APU 内的 SCU 之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL 的单元之间的一致性,PL 是做主机的。 3、高性能端口(High Performance Ports):四个高性能 AXI 接口,带有 FIFO 缓冲来提供“批量”读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在四个接口中 PL 都是做主机的。

Zynq开发

ZYNQ 的工程设计大体上可以分为 对硬件逻辑系统的设计 和 对 CPU 软件程序的设计

硬件逻辑系统设计:搭建一个满足用户需求的硬件环境,通过 Vivado 实现,verilog语言

CPU 程序设计:通过用户程序控制 CPU 工作,使整个系统达到预定的效果,该部分通过 Vitis 实现,c语言

两者间的关系及具体设计步骤如下图所示

本文章使用limfx的vscode插件快速发布