AD数据处理模块和数据包封装模块设计

AD 数据处理模块设计

模块结构

-

包含两个部分:数据缓冲;数据处理逻辑。

-

数据缓冲:对AD采集数据进行高速缓冲。

-

本部分采用

Ping-Pong FIFO结构,由2 * 64bits位宽、64深度FIFO组成。 -

FIFO运行在同步模式,即读写采用同一个时钟。写速率由AD输出数据速率决定,写入速率为

2M SPS,即一次写64bits,写入频率为2M;读取速率为100M * 64bits,读取速率远大于写入速率,可以采用同步FIFO实现。

-

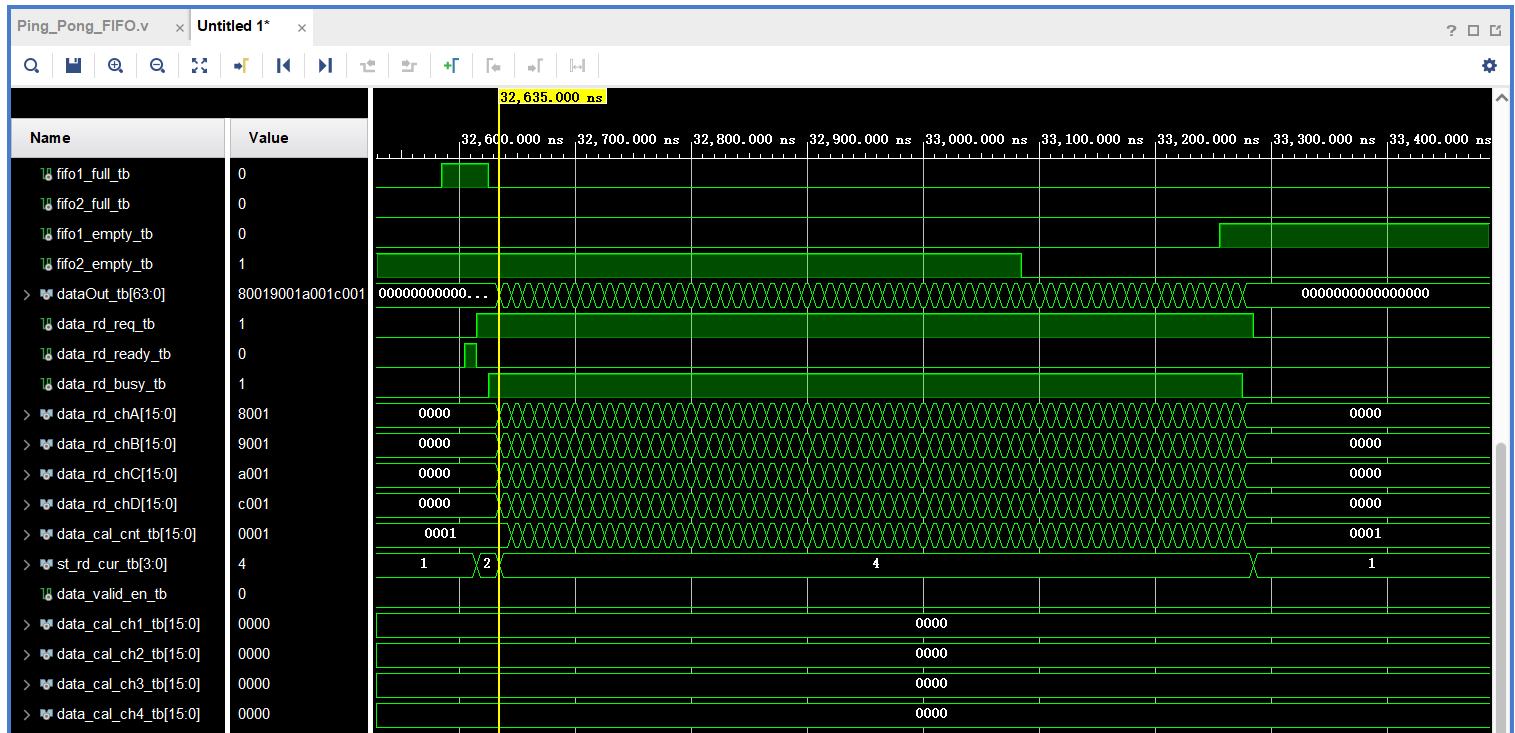

写入设计上,默认写入FIFO1,FIFO1写满后其Full信号拉高,状态逻辑切换到写入FIFO2。任意一个FIFO的Full信号拉高均会生成一个

data_rd_reday信号的高电平,用于通知后续数据处理逻辑读取当下已写满FIFO的数据。 -

读取设计上,默认处于

rd_idle状态,即所有FIFO读空时的状态。任意一个FIFO的Full信号拉高后,状态逻辑切换到读取该FIFO的数据状态。当任意一个FIFO的empty信号拉高时,表明数据读取完成,状态逻辑切换到rd_idle状态。

-

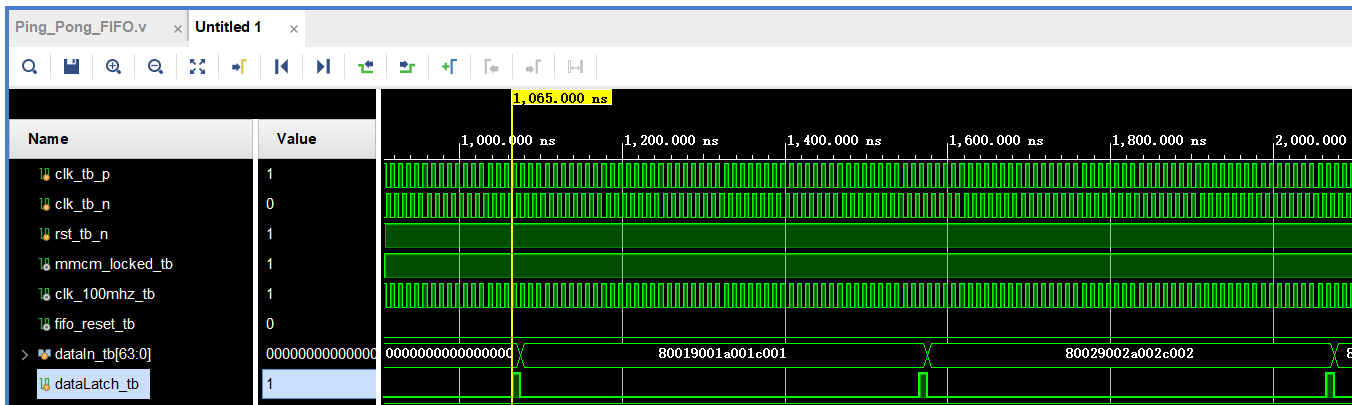

Ping-Pong FIFO的写入信号主要由AD_Latch信号生成,该信号具有一个时钟周期的高电平。AD_Latch信号为高电平时,在clk上升沿下完成一次AD输出数据的更新。 -

Ping-Pong FIFO的读取信号由后续的数据处理逻辑生成,为data_rd_req信号,当接收到data_rd_ready信号的高电平时,data_rd_req信号拉高,FIFO读使能,开始输出数据。

-

-

数据处理逻辑

-

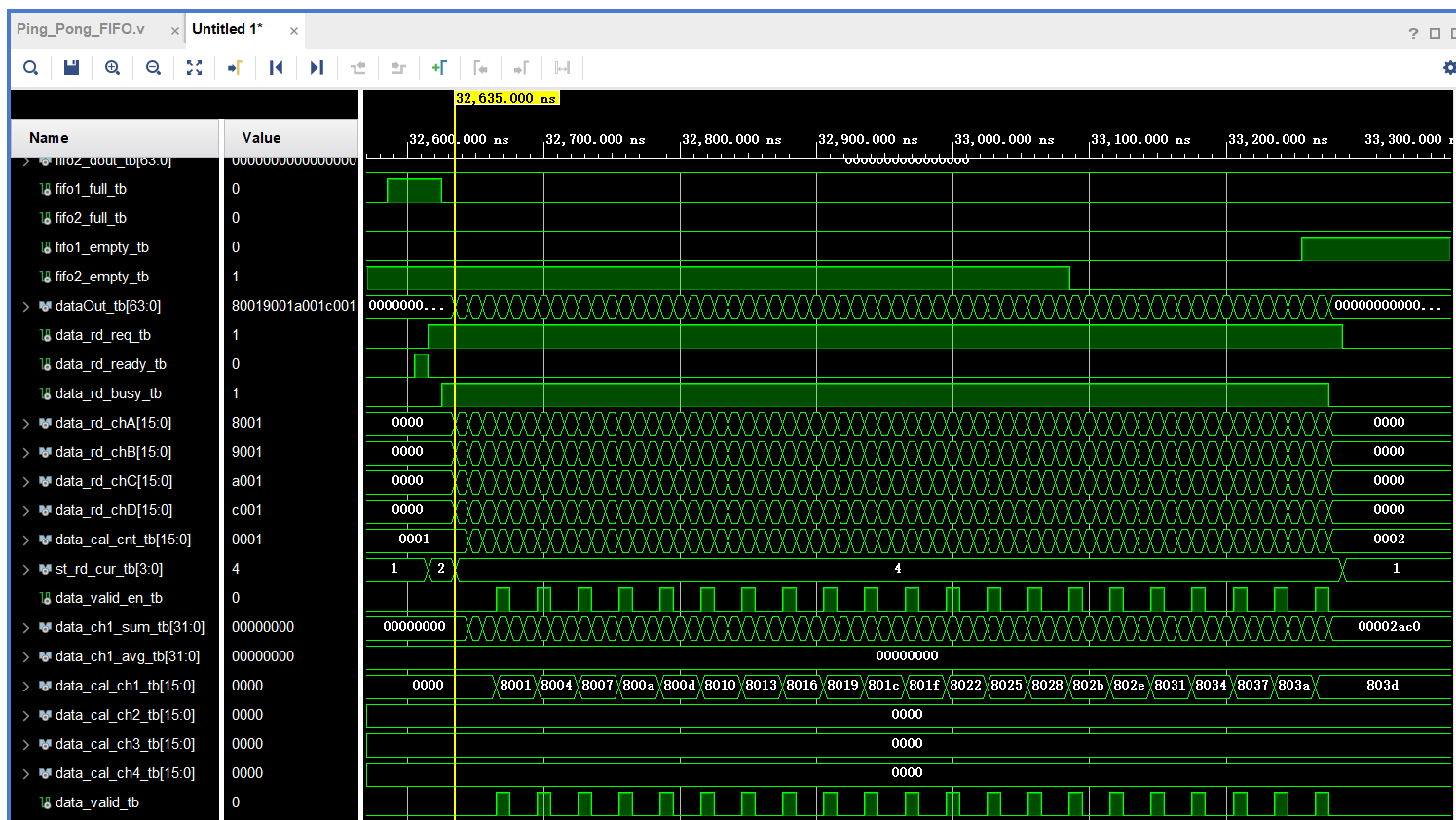

数据处理逻辑主要分为四个工作模式:停止,直通,抽取,平均。工作模式设定由内部参数控制,对该参数写入特定值设定该部分处于不同的工作状态。

-

输入信号为

Ping-Pong FIFO的64bits数据信号,以及一个data_rd_ready信号。输出为四通道16bits数据信号,以及一个data_valid信号。data_valid信号具有一个时钟周期的高电平,指示数据是否有效。 -

停止模式:该模式下四通道数据信号均输出

16h0000,同时data_valid信号拉低,表示没有任何有效数据。

-

直通模式:该模式下

Ping-Pong FIFO的数据全部通过数据处理逻辑,data_valid信号在整个数据输出的过程中保持高电平。

-

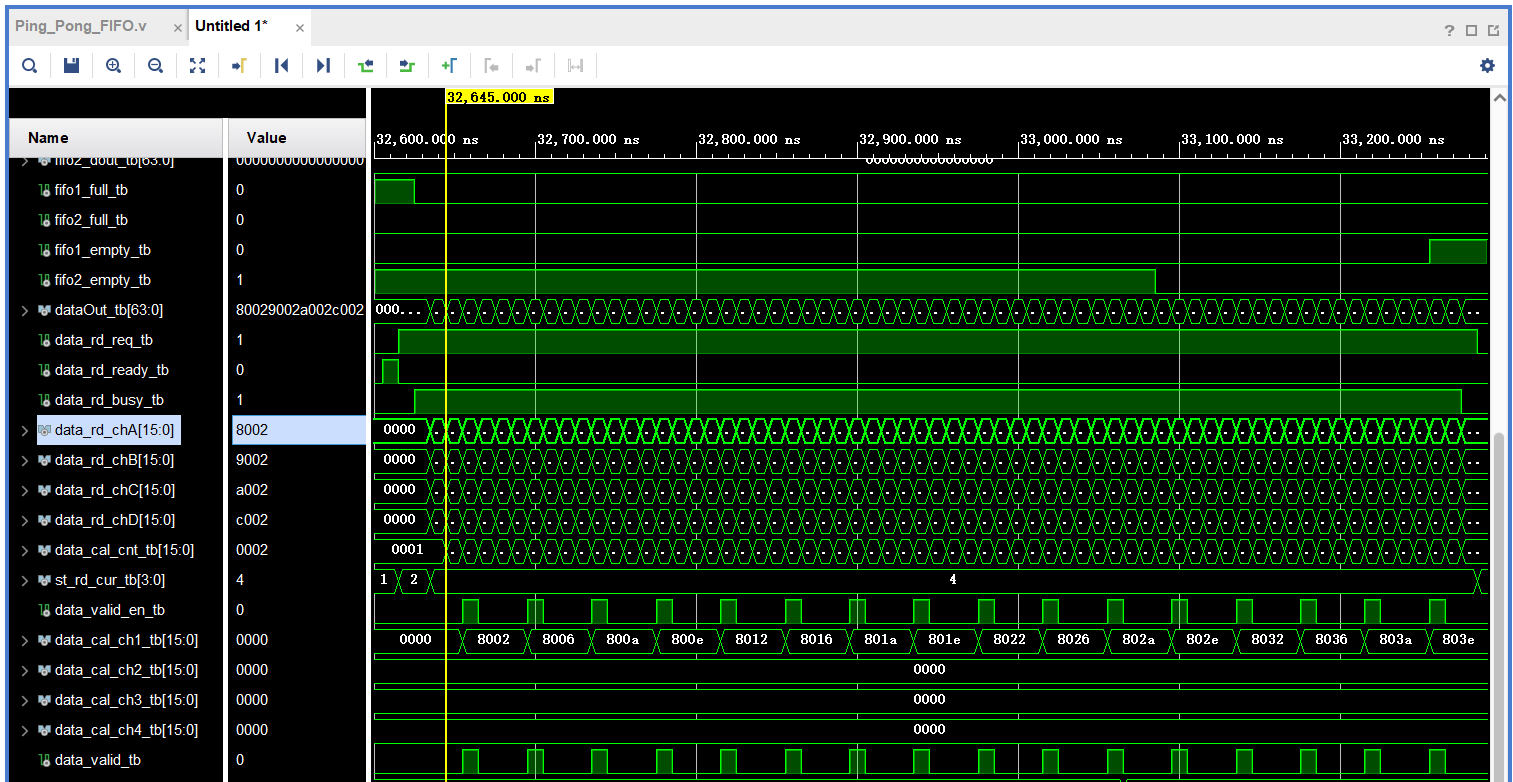

抽取模式:该模式下设置两个参数:

Num和Loc。Num参数用于设置需要从多少数据中抽取一个,Loc参数用于设置Num个数据中抽取哪一个。data_valid信号在四通道数据更新时产生一个时钟周期的高电平。下图设置为4:1抽取,抽取4个数据中的第2个。

-

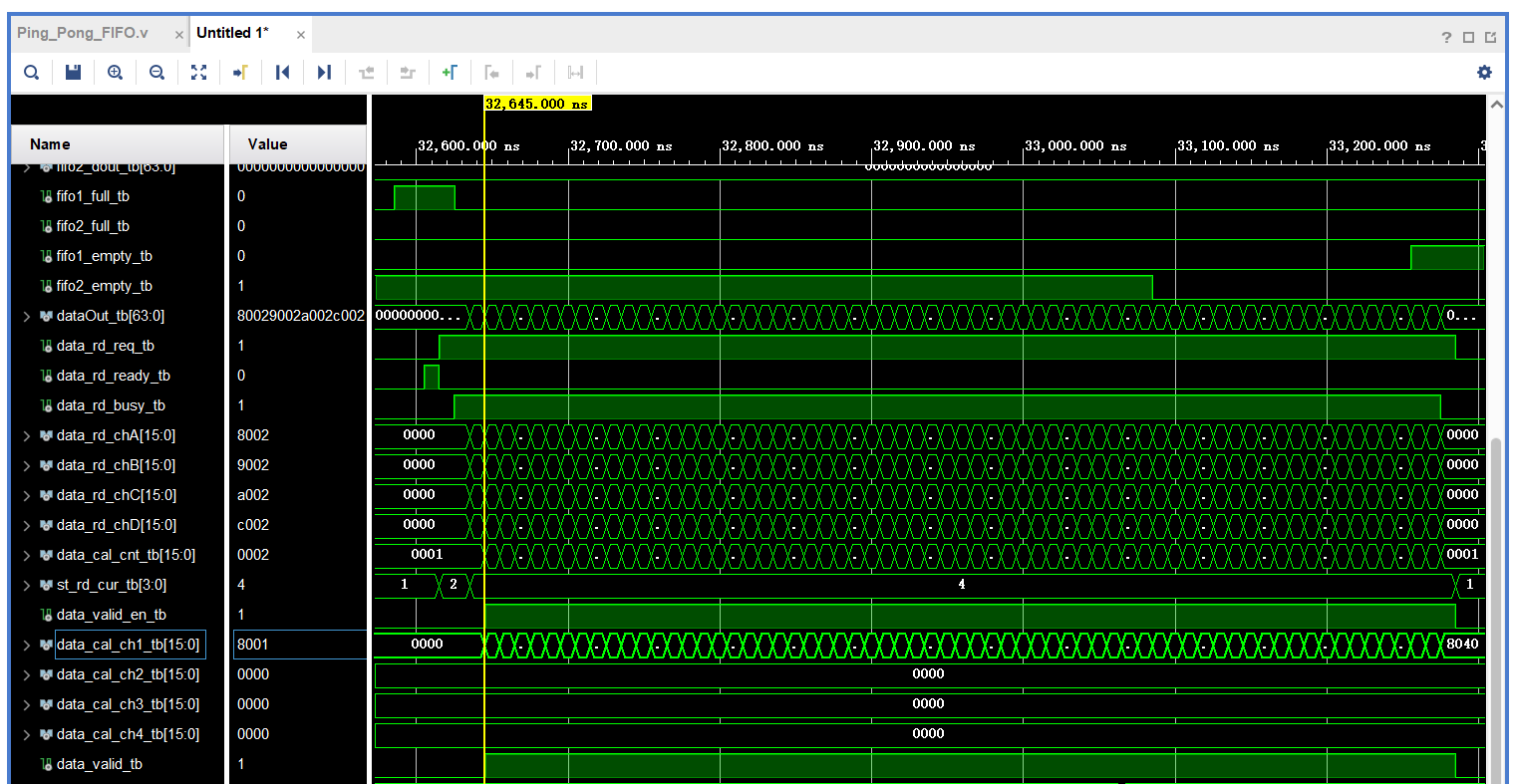

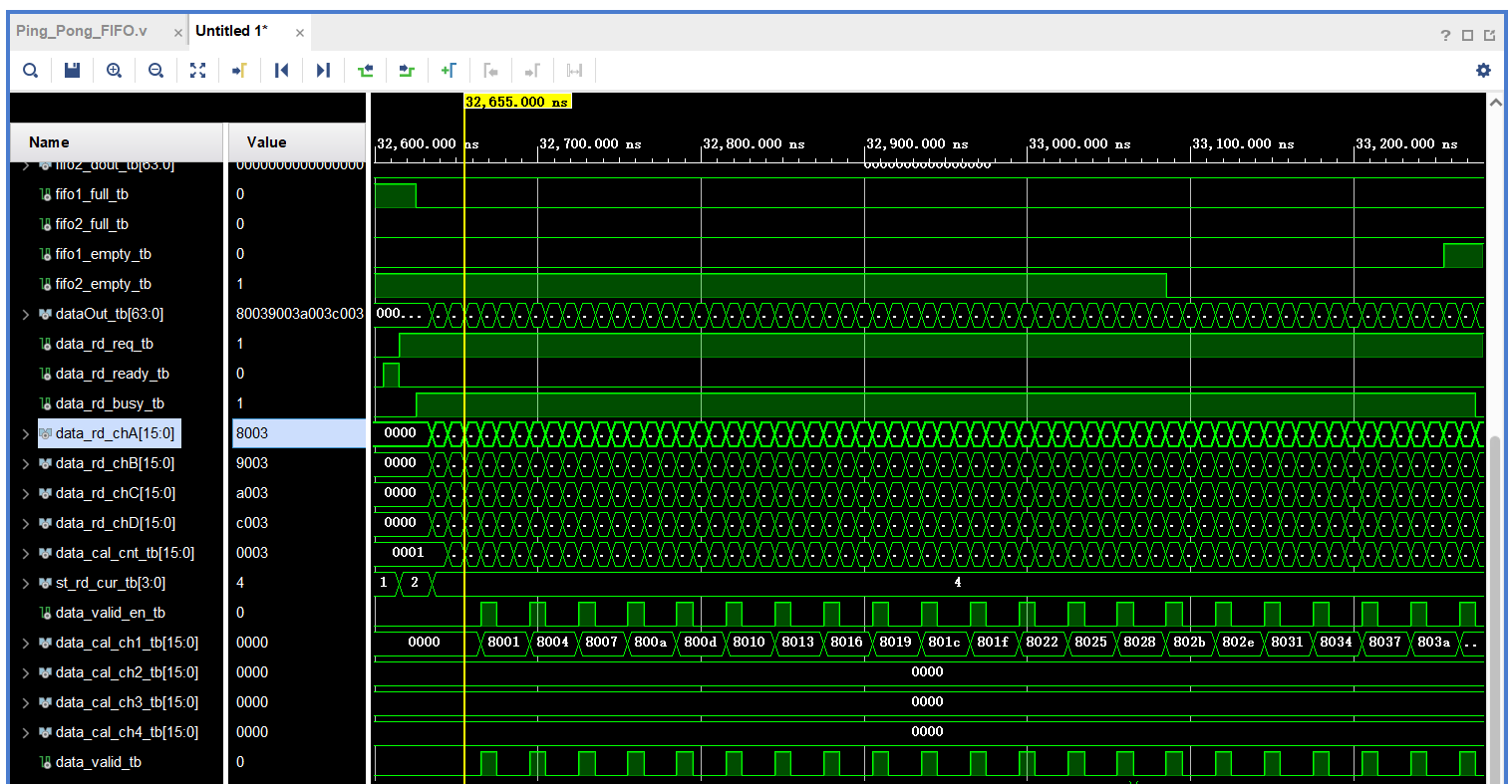

平均模式:该模式仅设置

Num参数,用于表示多少数据平均一次。平均方法为整数平均,为保证数据逻辑计算正确,方法为:Dout = Sum + Din/Num, Sum = Din/Num。同样data_valid信号在数据更新时产生一个时钟周期的高电平信号。平均模式采用整数除法,具有一定的误差。下图设置为3个数平均,为0x8001, 0x8002, 0x8003三个数平均。

-

AD 数据包生成模块设计

-

目前设计的数据包格式包括以下几个部分:

-

包头:128bits长度特定数,标识数据包开始,为

0xAA55AA55 0xAA55AA55。 -

包序列号:位于开始标识符之后。数据包序列号从1开始,具有32bits长度。

-

数据长度:位于包序列号之后。数据长度最小为1,最大不超过180。该参数也由用户设置,具有32bits长度。高于180后会出现数据包长度超过UDP单个数据包最大长度的限制,造成发送失败。180为设定仅发送4个通道的采样数据,如果增加通道数量,则该参数会进一步减小。

-

采样数据:单个通道为2个字节,按照ch1-ch2-ch3...ch_end的顺序排列数据,为一轮采样数据序列。最多可以发送多少个采样数据序列受到数据长度的限制。

-

包尾:128bits长度特定数,标识数据包结束,为

0xFF00FF00 0xFF00FF00。

-

-

数据包按照以上格式生成完成后,将采用

AXI-Stream接口,将数据流写入axis_async_fifo_adapter中。为匹配输入输出速率,数据包将采用64bits宽度。完成包尾生成后,状态逻辑生成一个高电平信号package_send_en,用于通知10G UDP协议栈开始发送。 -

需要注意的是,数据包生成模块运行于

100M时钟域下,10G UDP协议栈运行于156.25M时钟域下,需要对package_send_en进行跨时钟域处理,即在156.25M时钟域下对该信号进行23次同步。该步骤必须进行,会引入约1220ns的固定延时。

本文章使用limfx的vscode插件快速发布