一、使用Vivado配置Zynq的PS系统

前言

翻译内容有所简化,更多请看 原文: https://xilinx.github.io/Embedded-Design-Tutorials/docs/2023.1/build/html/docs/Introduction/ZynqMPSoC-EDT/3-system-configuration.html

正文

这一章展示了如何使用Vivado® Design Suite开发一个嵌入式系统,使用Zynq® UltraScale+™ MPSoC Processing System (PS)。

Zynq UltraScale+ 设备包括四核 Arm® Cortex™-A53-based APU、双核 Arm® Cortex™-R5F RPU、Mali™ 400 MP2 GPU、许多硬件知识产权 (IP) 组件以及可编程逻辑部分 (PL)。

这个产品提供了两种使用方式:

Zynq UltraScale+ PS 可以独立使用,无需连接任何额外的可编程逻辑 IP。

可以在可编程逻辑PL中实例化 IP 核,并将其附加到 Zynq UltraScale+ PS,形成 PS+PL 的组合。

案例 1:使用 Zynq UltraScale+ MPSoC 创建一个新的嵌入式项目

在这个示例中,您将启动 Vivado Design Suite 并创建一个项目,将嵌入式处理器系统作为顶层设计。使用的硬件开发板是zcu102,Xilinx公司官方的开发板。

设计输入和输出文件

这个示例设计不需要输入文件。我们将从头开始创建 Vivado 设计。该设计包括 MPSoC 的处理系统模块。在这个示例设计中不会添加可编程逻辑 IP,因此此设计无需进行实现和比特流生成。

这个示例设计的输出是硬件配置 XSA 文件。它将用于进一步的软件开发。

输入:无

输出:edt_zcu102_wrapper.xsa

创建Block Design项目

打开Vivado,创建一个新项目后

在Flow Navigator窗格中,展开IP integrator并单击Create Block Design

使用以下信息在“创建块设计”向导中进行选择

Screen | System Property | Setting or Command to Use |

|---|---|---|

Create Block Design | Design Name | edt_zcu102 |

Directory | <local to Project> | |

Specify Source | Set Design Sources |

单击OK。Diagram视图打开并显示一条消息,指出此设计为空。下一步是从目录中添加一些IP

单击“add IP”

在搜索框中输入zynq,查找zynq IP

双击Zynq UltraScale+ MPSoC IP将其添加到块设计中

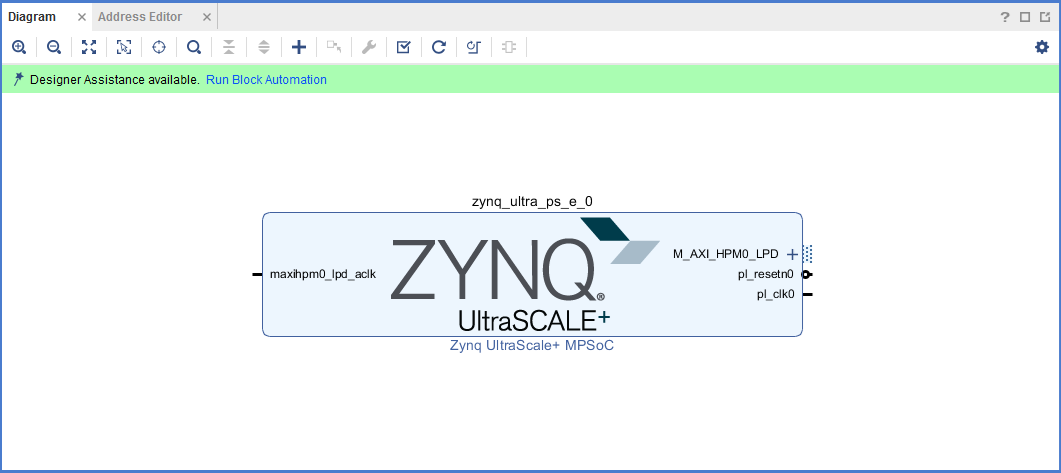

Zynq UltraScale+ MPSoC处理系统IP块出现在Diagram视图中,如下图所示

在Vivado中管理Zynq UltraScale+处理系统

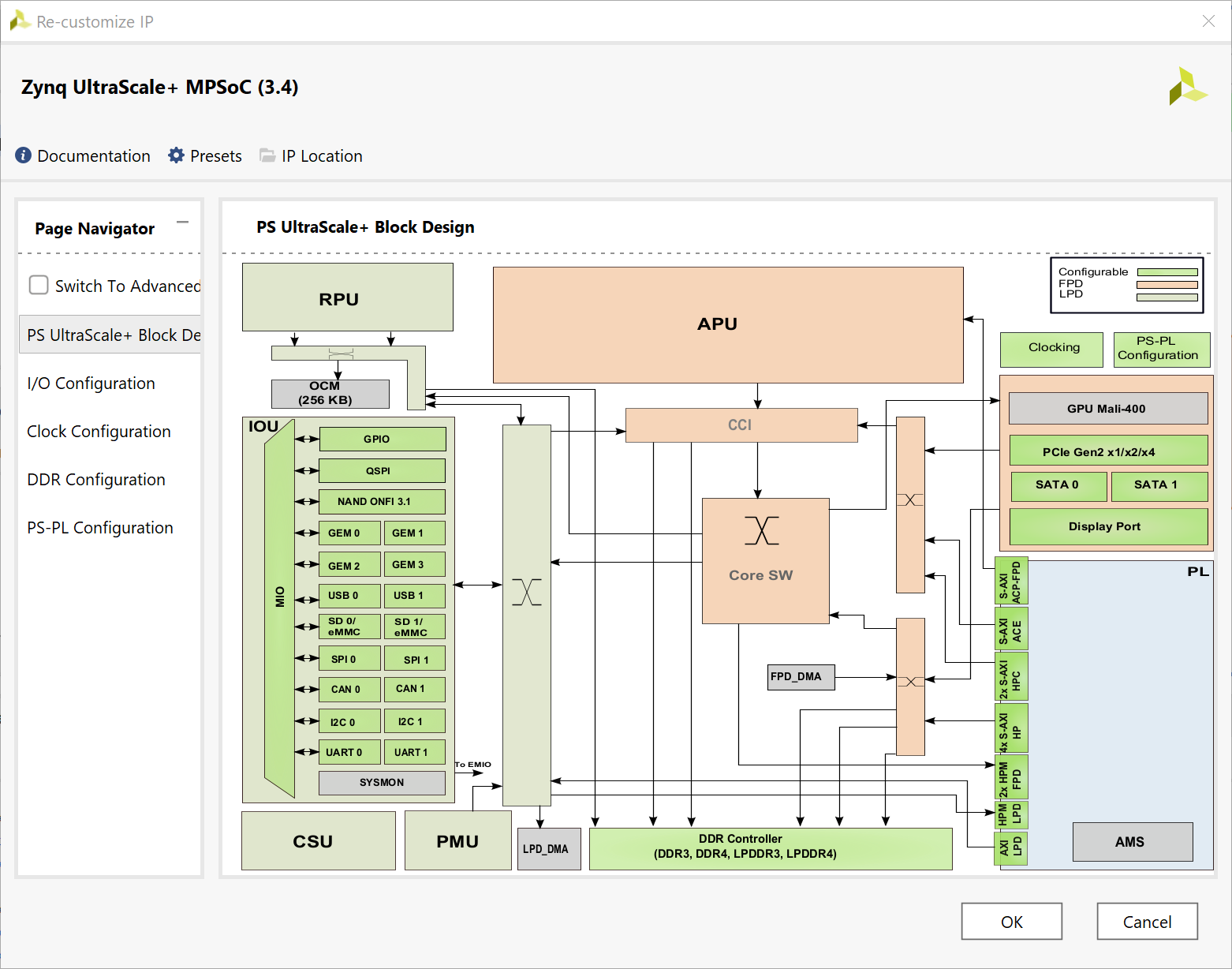

在“框图”窗口中双击Zynq UltraScale+ Processing System模块。进入“重新定制IP”视图,如下图所示。注意,默认情况下,处理器系统没有连接任何外设

根据你所使用的开发板的配置来配置Zynq UltraScale+ PS IP核,这里教程由于使用的是官方开发板,点击“Run Block Automation”可以一键配置

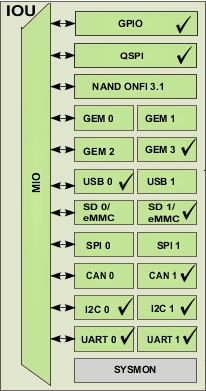

自动配置好IP后重新点进IP配置页,看到外设旁边打了一个 √ ,表示该外设已配置正确

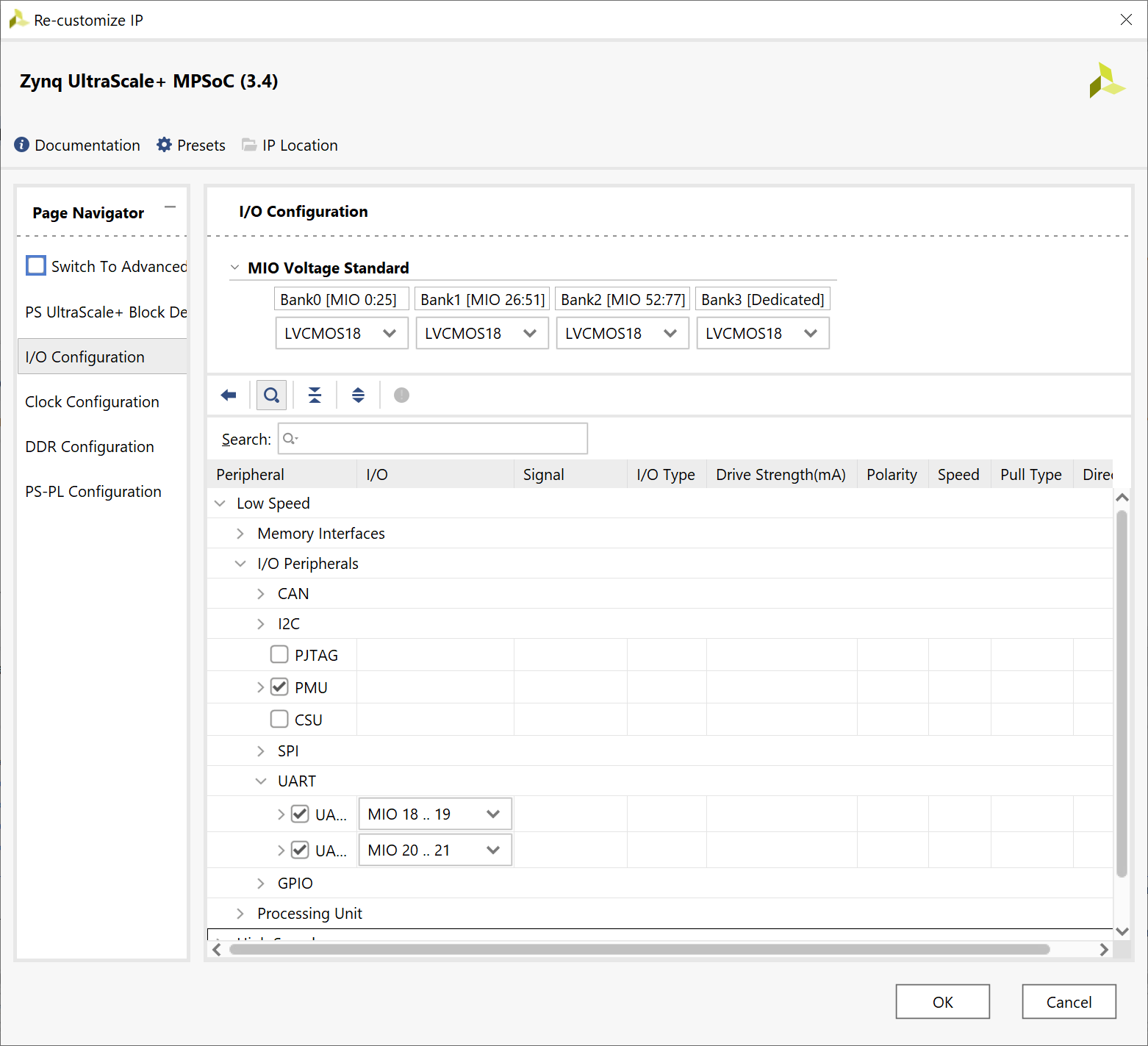

在框图中,单击其中一个绿色的I/O外设,如上图所示。打开所选外设的I/O Configuration视图。如果不能一键配置,就是在该页面中配置外设的

在页面导航器中,选择PS-PL Configuration,展开PS-PL Interfaces 选择项,再展开Master Interface选择项。PS-PL AXI 主接口在默认板设置中启用 AXI HPM0 FPD 和 AXI HPM1 FPD。 本案例从仅包含 PS 逻辑(无 PL)的设计开始,因此可以禁用 PS-PL 接口。即取消选择“axis HPM0 FPD”和“axis HPM1 FPD”

点击“OK”来完成Zynq UltraScale+ PS IP核配置

验证设计,创建Wrapper和生成Block Design

右键单击Block Diagram视图的空白区域并选择Validate Design。也可以按“F6”键。 提示“验证成功,在此设计中没有错误或严重警告”对话框。

在"Source"导航窗中右击"edt_zcu102.bd",选择Create HDL Wrapper选项,然后点击"OK"

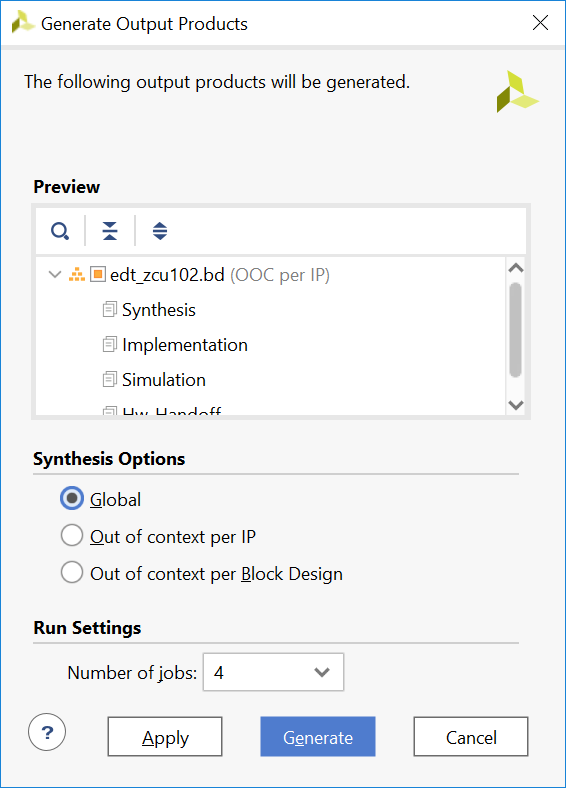

Flow Navigator -> IP INTEGRATOR中点击选项"Generate Block Design",如下

导出XSA文件

在菜单栏中选择 File → Export → Export Hardware

单击 Next

选择Pre-synthesis ,单击 Next

输入 XSA 文件名和导出地址,Next,Finish

这里导出的XSA文件将会在下一章Vitis开发中使用

本文章使用limfx的vscode插件快速发布