所有模块整合与延时初步测量

模块整合

-

原有设计包含以下几个模块:

-

ADC读取模块;

-

AD数据组blob模块;

-

blob缓存并发送到UDP网络模块;

-

UDP-IP-MAC三层网路模块;

-

以太网PHY模块。

-

-

现有设计中,采用一个

AD_BLOB_UDP_TOP模块将所有模块整合,对外只暴露以下接口:-

全局时钟与复位输入,加入

clock_reset模块生成ADC模块所需100MHz时钟和以太网PHY模块控制所需125MHz时钟,以及以上时钟对应的复位信号。 -

ADC对接信号,即ADC时钟和ADC数据接口。信号目前为LVCMOS型,如果数据速率需要升级则需要加上IO转换模块转换到差分接口。IO转换模块只需要调用

IBUFDS、OBUFDS即可。 -

以太网PHY相关信号,直接对接高速收发器和GTH专用时钟芯片的时钟输出引脚。

-

所有模块需要配置的、可变的参数,如

采样周期、采样长度、ADC通道数、IP地址、MAC地址等等。

-

-

此外还修改了blob generator模块的配置信息的发送流程。

-

第一次运行时由于不知道目标电脑的IP与MAC地址,因此需要先发送一个包含配置信号的UDP包,触发ARP查询包发送。接收到目标电脑的ARP回复包后,即可进入正常的读取AD数据并组blob状态。

-

发送配置信息流程为:采用一个计数器,没有收到正确的ARP回复包时计数器递增,到设定值时触发配置信息的发送,然后计数器清零,循环,直到接收到正确的ARP回复为止。

-

原有发送流程为必须等到配置信息发送流程结束后才能进行状态跳转,进入到读取AD数据组bolb状态。会出现发送一次配置信息后,即使接收到ARP回复,也会继续处于等待发送配置信息状态,直到配置信息发送完成。

-

现有改进修改了状态跳转流程,接收到ARP回复后直接跳出等到配置信息状态,直接进入读取ADC数据组blob状态。

-

延时初步测量

-

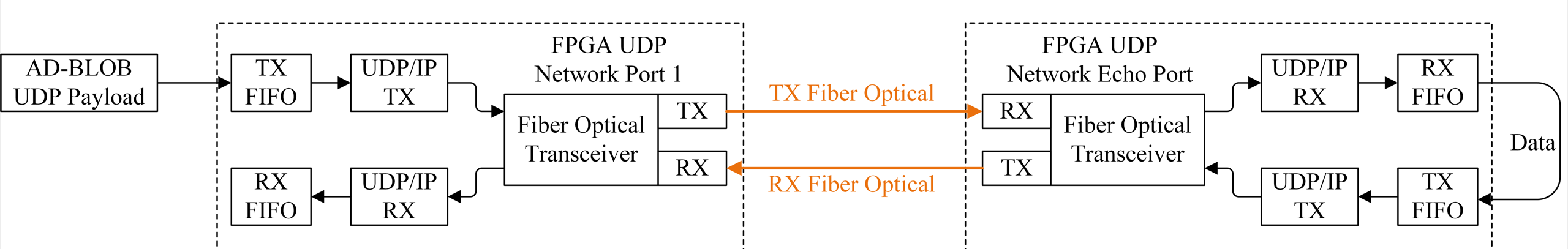

测量方法为采用两个UDP网络:

-

第一个UDP网络对接

ADC读取、AD数据组blob模块、blob缓存转udp发送模块,主要发送ADC blob包。 -

第二个UDP网络工作于

Echo模式,将接收到的UDP包返还给第一个UDP网络。 -

第一个UDP网络的TX-RX延时即为网络的 RTT时延。当UDP网络发送头部数据时,

udp_tx_rx_delay信号拉高;当接收到数据包的头部数据时,udp_tx_rx_delay信号拉低。高电平时间即为RTT时间。

-

-

测试结果如下。 、

-

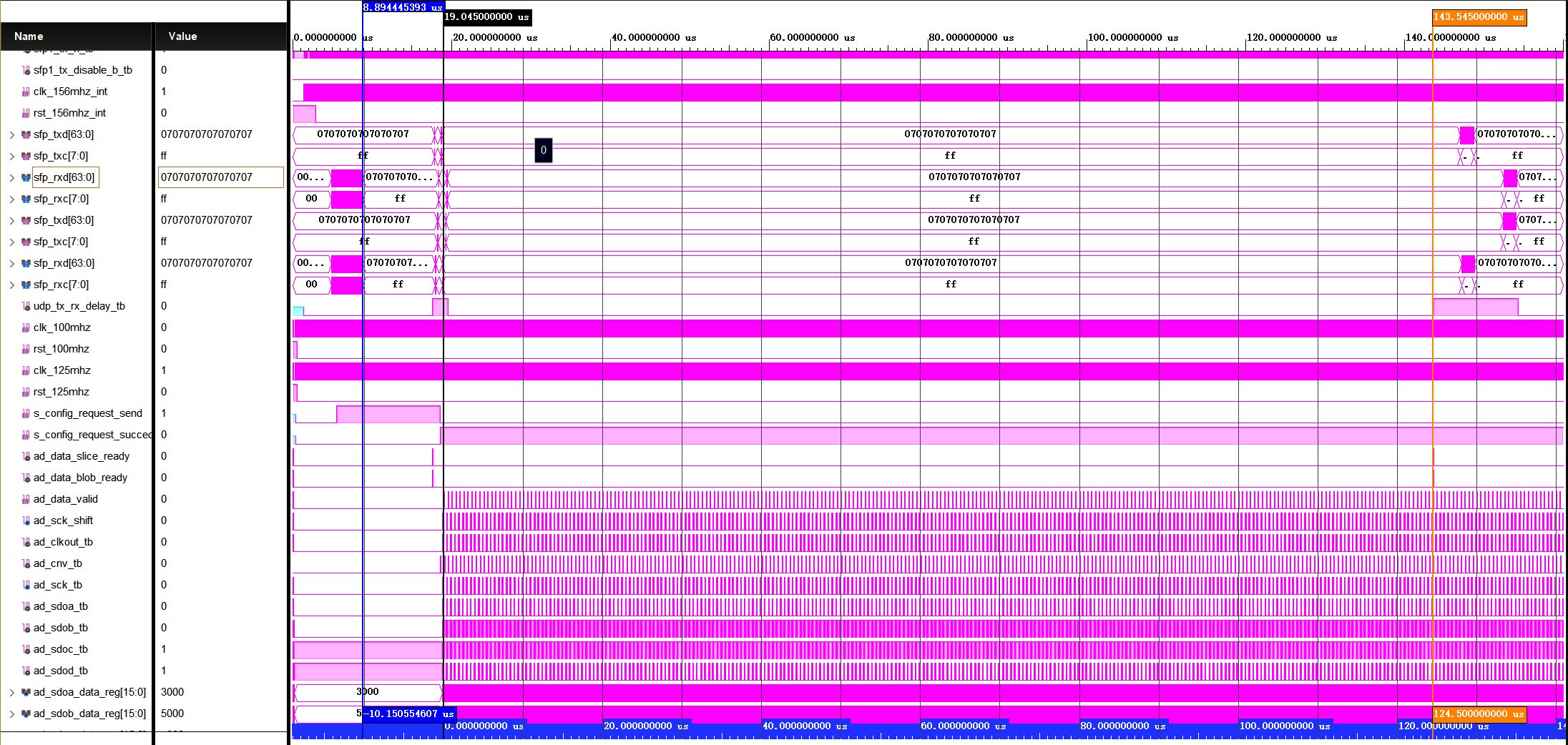

设定ADC采样周期为

500ns。设定ad组blob模块单次接收250次采样,一次采样包含4个ADC通道,则总的blob长度为8 + 250*2bytes*4 = 2008bytes。采样从19.045us开始,到143.545us时组blob结束,时长124.5us,对应124.5/0.5 + 1 = 250个采样点,ad组blob模块工作正常。

-

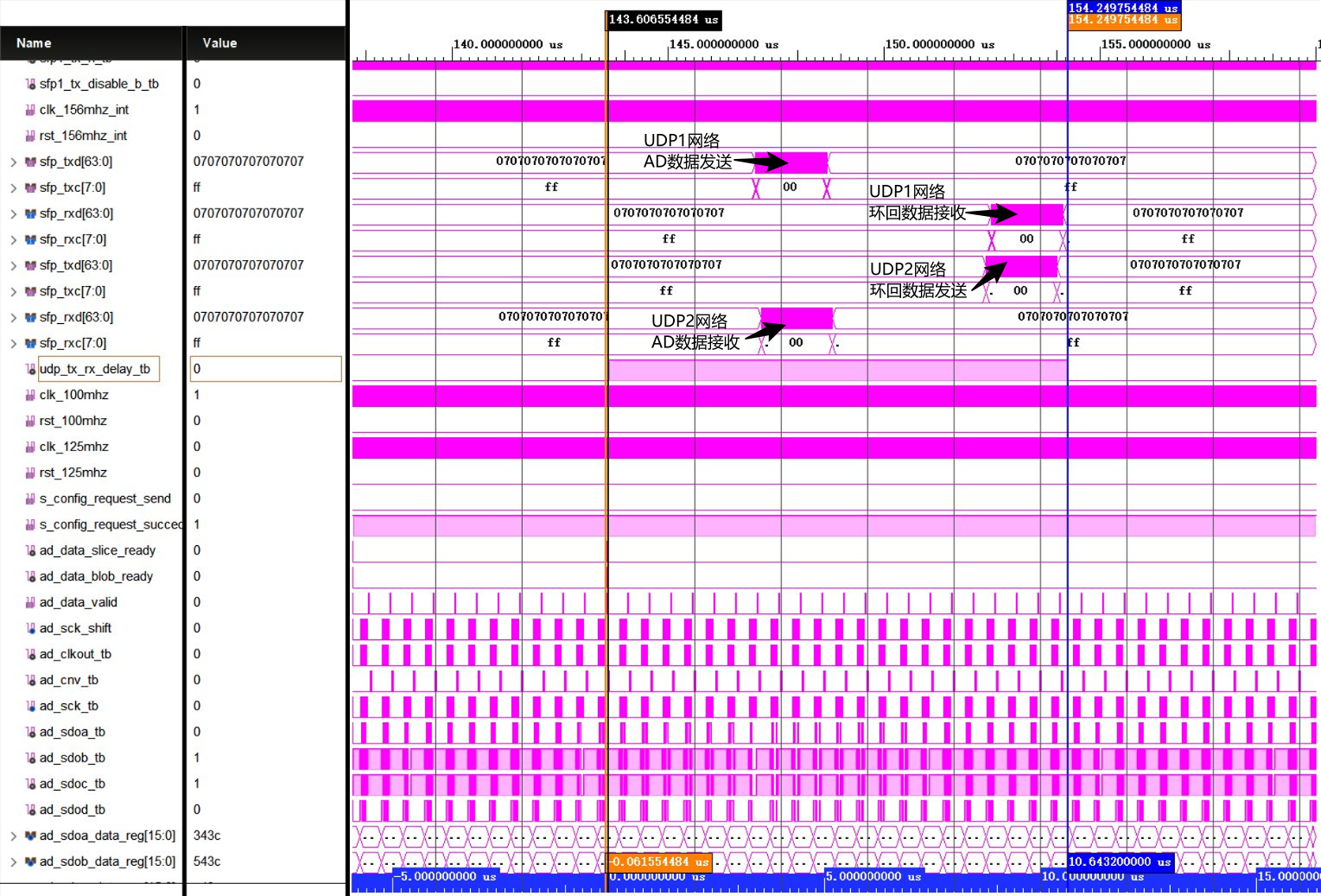

143.606us处启动UDP发送。143.545us AD组blob结束到143.606us UDP开始发送,中间的时延为发送开始信号跨一次时钟域,需要数个时钟周期。测量得到

ad_tx_rx_delay高电平持续时间为10.643us,则RTT时间为10.643us。若采用自环,则RTT时间为5.322us。具体测试还需要上板、采用示波器测试。

-

最早一次单个UDP网络自回环测试中,因为当时对发送流程不熟悉,导致对同一个UDP包的发送边沿和接收边沿的识别有误,需要在原有的测试结果上加上

3次UDP数据包进入FIFO的时间,3次进入FIFO主要为UDP checksum生成,TX CRC32校验生成,RX CRC32校验。取UDP数据包进入1次FIFO的时间为一个发送周期,即1.242us。加上3次FIFO时间后的得到

-

修正后的发送与接收流程如下,计算得到单个UDP网络自回环时间为

3*1.242 + 0.487 = 4.213us。当时测试用的数据包长度为182*8 = 1456bytes。认为RTT时间与数据量呈线性关系,忽略截距,则换算到2008bytes时RTT时间为5.81us,与上面测试相近,说明修正后发送流程与实际较为贴近。

-

本文章使用limfx的vscode插件快速发布