整机测试与论文工作

整体工程上板测试

-

将整个工程的ADC输入输出、收发器输入输出、时钟、复位等信号与FPGA引脚绑定后,进行综合、实现、生成bit流文件后,烧录到板子上进行测试。本次测试在FPGA上构建了两个UDP网络:

-

AD数据传输UDP网络,MAC地址为

02:00:00:00:00:00,IP地址为192.168.1.128,端口是1234。 -

UDP Echo端口网络,MAC地址为

5A:51:52:53:54:55,IP地址为192.168.1.10,端口为8010。主要用于与AD数据传输UDP网络构成回环网络,测试RTT时间。 -

电脑端采用与UDP Echo网络相同的网络参数配置,用于接收来自底板的AD数据。实际测试使用的是WireShark抓取网络包获得UDP包内的Blob数据。

-

-

AD数据传输流程如下:

-

上电或者复位时由于缺少目标电脑的IP地址,需要先发送ARP请求包。

-

采用先发送一个包含ADC、Blob生成等信息的UDP包触发ARP请求包发送。上位机检查ARP请求包的IP地址,是本机就返回ARP回复包。

-

AD数据传输UDP网络接收到ARP回复包后,正常进入UDP发送流程。此时触发ARP请求的UDP包会被正常发送。后续切入到AD数据发送。

-

-

ADC与组blob配置参数如下:

-

ADC采样率为250khz,最高2MHz。4通道全部开启,单个通道输出16bits。

-

组blob,设置UDP payload长度为2008,单个blob采样点长度为250点,则单个blob包含8个bytes的头部信息后长度为2008,可以在一个UDP包传递完成。这样使得一个blob仅由一个slice组成。

-

触发ARP请求的UDP配置包发送时间间隔为

200,000,000,乘上10ns的时基为2s。由于在没有目标电脑的MAC情况下,UDP配置包最多只能发送11 ~ 12次,多了协议栈就不能继续接收待发送的UDP数据包,因此这个时间需要尽可能大。

-

-

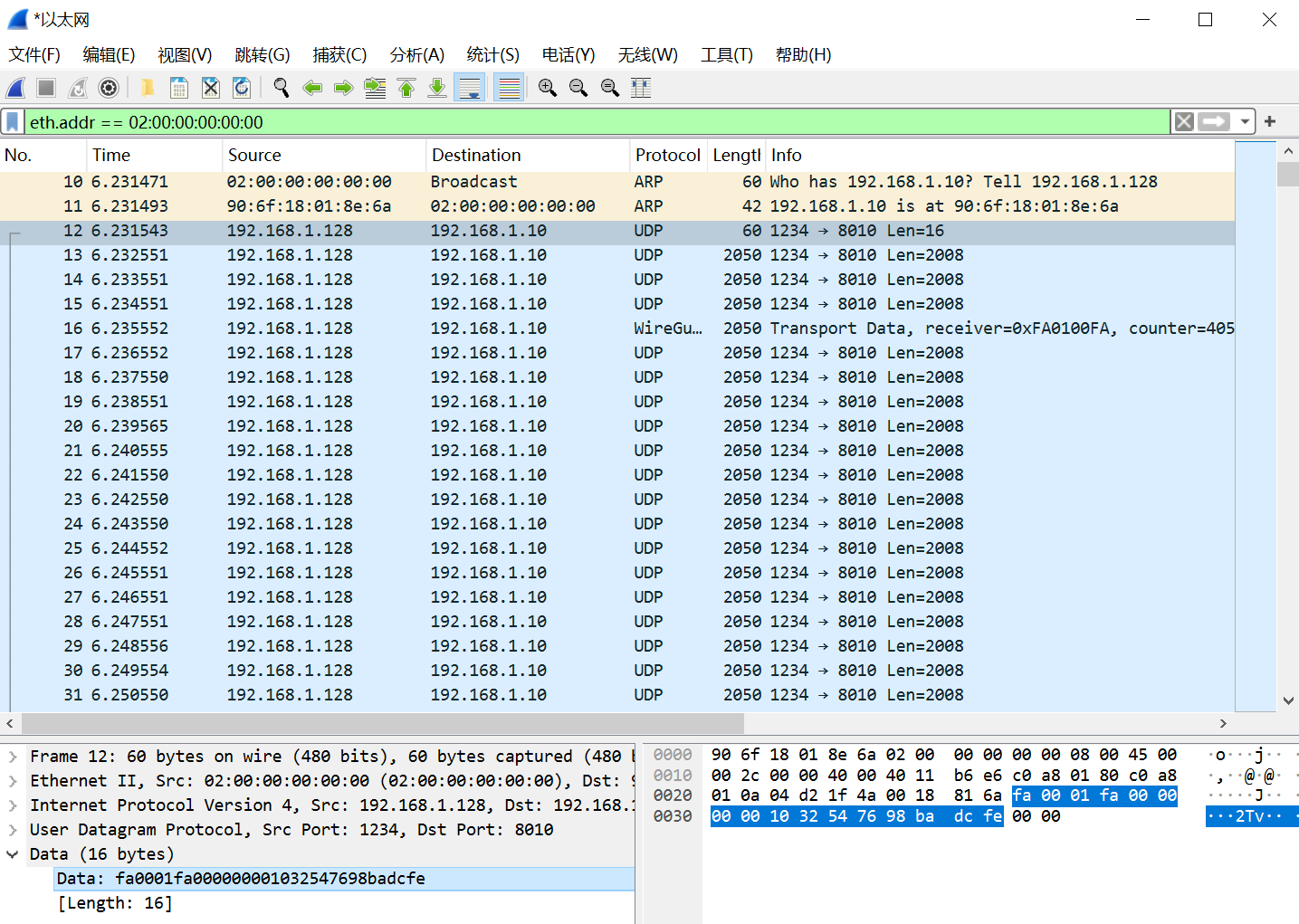

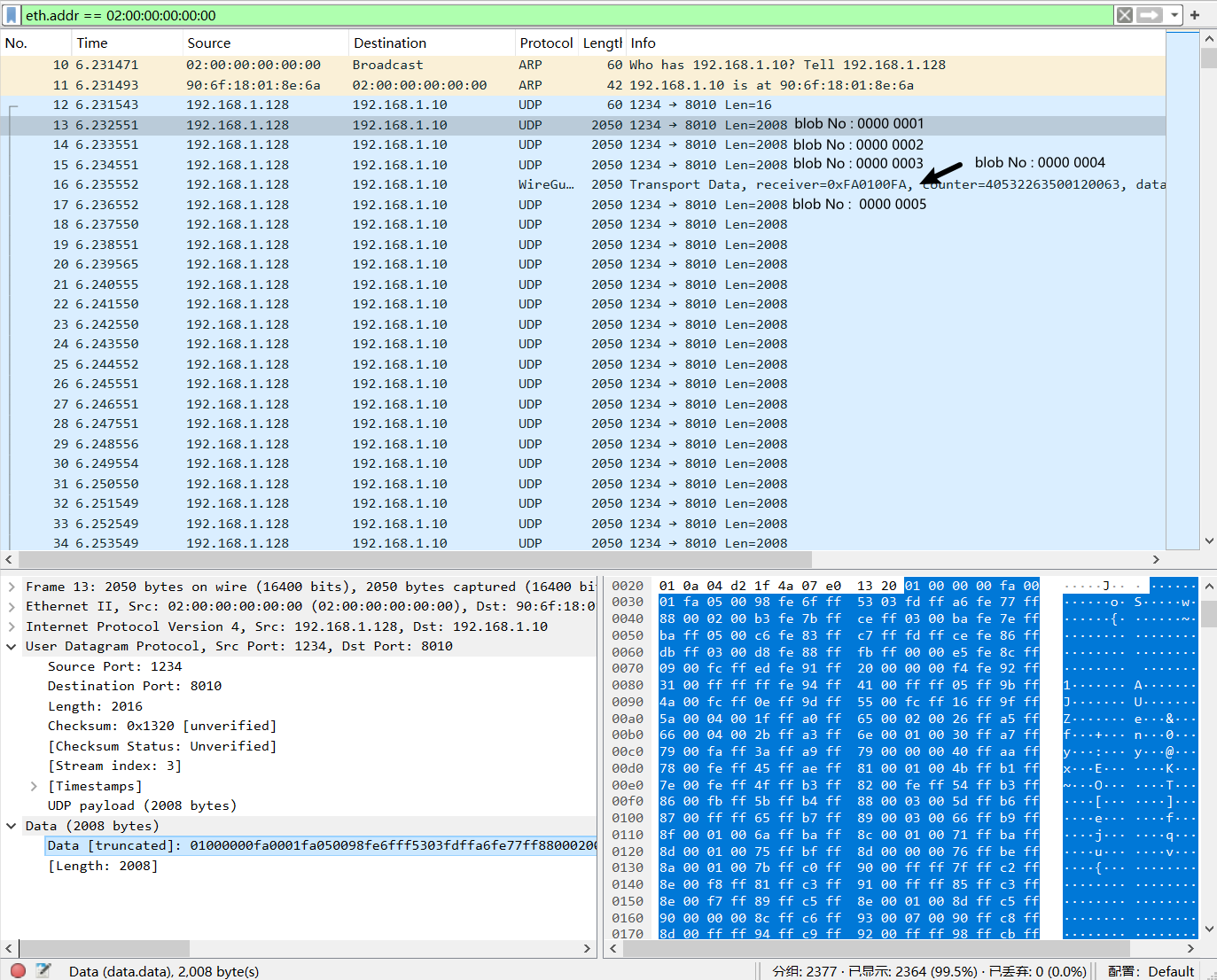

采用wireshark进行抓包。设置

eth.addr==02:00:00:00:00:00,只抓取来自AD数据输出UDP网络的包。流程如下。

-

第一个包是

broadcast ARP请求包,采用广播的方式请求网络内部192.168.1.10的MAC地址。 -

第二个包是

ARP回复包,为本机电脑的网卡MAC地址。 -

第三个包是

触发ARP请求包的UDP数据包,payload内容为fa0001fa00000000 1032547698badcfe。网络传输字节方式为大端模式,FPGA上UDP网络单次发送8个bytes,将payload内容按大端模式排列,高为在前,低位在后,为:-

第一次发送字节为

000000 00 FA 01 00FA,最高位三个字节000000表示没有用到该部分。 -

第二个字节

00表示最后一个slice的采样点长度为0, -

第三个字节

FA表示最后一个字节前的slice内包含的采样点长度,为250; -

第四个字节

01表示当前blob内仅包含一个slice。为其他数则表示有多个slice。 -

第五个部分为

00FA,表示当前blob内包含多少个采样点。由于当前blob内仅一个slice,此部分与第三个字节相等。 -

第二次发送的字节为

fedcba9876543210,主要作用为使得配置信息UDP包的长度满足16字节。后续需要扩展UDP配置信息包的长度,修改这部分即可。

-

-

后续全部为AD数据组成blob后发送的UDP包。一个包的数据长度为2008,与设置匹配。blob编号从

0000 0001开始向后递增。

-

-

数据包的处理采用matlab进行。wireshark导出一个包的分组字节流为txt文件,matlab读取该txt文件。

-

由于wireshark导出的分组字节流包含地址和字符信息,需要在matlab中去除。分组字节流中,两个空格字符间为AD传输的数据。

-

matlab将payload中的字节组成一个长字符串。网络传输中两个字符表示一个字节,matlab会将一个字节拆分为两个字符。对于AD数据读取,一个字节需要读取两个字符。字符统一用

hex2dec函数转换为无符号十进制,对于包含符号位的AD数据,需要做一次转换。 -

前16个字符为当前UDP包内的slice和blob信息,包含blob编号,blob内采样点长度,slice编号,slice采样点长度。此部分可以修改。

-

后续所有字符为采样数据,按照每16个字符为一个采样点进行读取。单个采样点包含4个通道,每个通道4个字符。通道读取顺序为

1-2-3-4顺序进行。由于网络传输字节时按大端顺序,需要对2字符组成的字节进行顺序切换,使高位在前,低位在后,后续使用hex2dec和符号转换才能得到正确的数。转换出的结果为AD输出的16bits数对应的带符号十进制数。 -

绘制

blobNo=0000 0001的包,即第一个包的采样数据转换结果,如下。由于没有接信号,所有通道均没有有效的波形。ch1上仅有个位数的数据波动。ch2-ch4由于没有接对应的模拟前端电路,开始采样前存在采样端电容的充放电现象,表现为过渡过程。后续读数接近稳定。

-

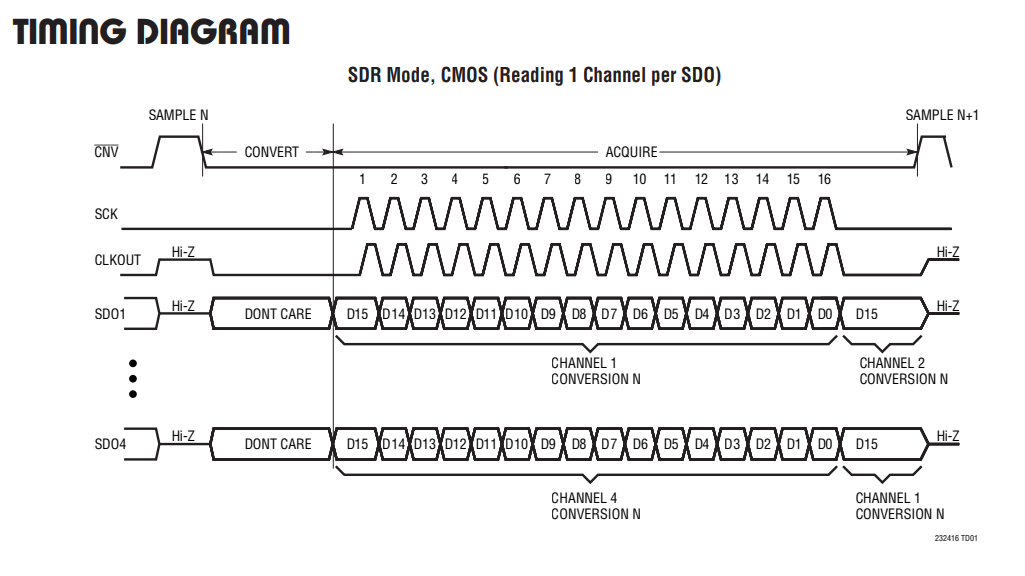

ADC数据读取架构分析

-

现有ADC数据读取架构为ADC输出与数据同步的时钟,即SDO1-SDO4数据线需要在

CLKOUT驱动下读取。

-

CLKOUT为ADC输出到FPGA的时钟。外部时钟输入到FPGA需要消耗FPGA的

GCLK资源,即通过专用的GCLK接口和对应的时钟处理模块后才能进入FPGA的时钟网络中,驱动其他逻辑。 -

FPGA资源一般按

Bank划分,对于Xilinx的FPGA,每个Bank一般提供4个GCLK输入。目前使用的FPGA核心板上可用于传输ADC数据的bank一共3个,总共12个GCLK,允许12个外部时钟输入。 -

对于目前的ADC数据读取架构,一个时钟对应4个通道。当下的ADC数据读取架构下和ADC芯片下,12个GCLK最多可以实现

48个通道的数据读取。需要扩展通道则需要更改ADC数据读取的架构。 -

官方给的例程没有采用CLKOUT为数据源时钟,而是采用

Altera的PLL输出相位、占空比均可调的时钟信号,使这些时钟信号与SDO1-SDO4的时序匹配,进行读取。以上方法存在许多问题:-

Xilinx的PLL与MMCM不支持相位可调的时钟输出。

-

本质上同样消耗时钟资源,而且PLL资源不如GCLK资源多。

-

没有源时钟同步,每个ADC芯片都需要精细调整对应的读取时钟的

相位、占空比参数,极其麻烦。

-

-

DTACQ的ADC数据读取方案目前未知。目前从它们公开的资料可知,FPGA型号为

XC7Z030-FBG676,相关配置如下:-

2片DDR3 DRAM,应该是仅连接到PS侧,用于Linux系统运行使用。PL侧没有任何DDR。

-

4个6.6Gb/s的收发器,运行5Gbps以太网。

-

PL侧5个bank,共20个GCLK。

2M 64ch配置为每个通道1个ADC。如果所有ADC均采用对应源时钟进行读取,则GCLK资源远远不够。推测它们的ADC模块架构如下:-

FPGA输出一路源时钟和CNV信号,采用缓存芯片一分为8,驱动8个ADC。

-

ADC读取时采用某个ADC输出的源时钟作为数据参考时钟。这路时钟英是时序或者延时性能最差的时钟。

-

-

2M采样率最高提供64通道,1M提供192通道。1M版本的ADC采集模块上用了一个LQFP封装的Xilinx芯片,推测是Xilinx的

CPLD芯片,因为Xilinx的FPGA都是用的BGA封装。CPLD应该完成ADC和FPGA的各种交互信息的逻辑操作。

-

-

后续如果需要增加ADC通道、ADC采样速率,需要更改ADC采集架构。

-

一种方法是采用推测出的DTACQ方法,采用某一路时钟作为源时钟。但是ADC源时钟时序存在漂移,会随时间、温度等因素产生变化,不容易预测。

-

在ADC与主FPGA间增加一个FPGA作为数据中继。多通道ADC的低速数据先被中继FPGA收集,中继FPGA再通过高速总线如

多路LVDS与主FPGA进行通信。中继FPGA会放置在采集模块附近。此方法主要是工作量大,但可以保证通信与数据质量。

-

毕业大小论文

-

大论文主要分为以下几个部分:

- 绪论

1.1 课题研究背景与意义 1.2 研究现状分析

1.3 主要研究内容和章节安排 - AD采集模块设计

2.1 ADC采集模块总体架构设计

2.2 ADC采集模拟前端设计

2.3 ADC芯片选择与外围接口设计

2.4 ADC模拟前端部分仿真

2.5 ADC在FPGA内部控制设计 - 采样数据流处理

3.1 采样数据流处理需求分析

3.2 采样数据流处理部分架构设计

3.3 采样数据流传输接口研究(主要分析几种接口,选择现有接口)

3.4 采样数据流组blob设计 3.5 采样数据流缓冲设计 - 基于UDP的实时数据传输网络构建

4.1 数据传输网络协议研究(主要侧重延时部分)

4.2 基于UDP的实时数据传输网络架构设计

4.3 UDP网络数据发送流程设计 - 测试与分析

5.1 ADC采集模拟前端测试(主要为线性度测试)

5.2 ADC数据转换测试(连接AFE,测试交直流精度)

5.3 采样数据流测试(连接UDP网络,在电脑上读取数据包,绘图测试)

5.4 UDP数据网络传输时延测试(FPGA上两个UDP网络回环,改变数据包长度得到不同延时) - 总结与展望

6.1 现有工作总结

6.2 展望(PS侧走AXI配置各个模块的工作参数,上位机数据接收和处理程序编写)

- 绪论

-

小论文总体结构与大论文类似,不同在于各部分填充内容不一致。

-

南网中文:绪论部分参考中期和开题,各个模块设计主要给处设计的原理图和状态机转换图,不会写太详细。测试结果只给

线性度测试和最大延时测试两个结果,以及绘制一个UDP数据包采样波形图。 -

毕业用小论文:基本参考大论文各个部分内容,设计部分会写得简单一些,测试部分基本相同。

-

投期刊对面可能会问的几个问题:

-

整个采集装置或设备的实物图有没有?

-

有没有放到J-TEXT装置上连接几个诊断测试的数据波形图?

-

有没有配套的上位机驱动或数据读取软件?

-

-

感觉投稿小论文的时候这个采集只做到验证机的程度,不能算原型机,暂时没有达到能够实际放到装置上用的程度,可能会被卡。

-

等走完所内流程预计最快3月初可以投,辅导员那边说的是到5月底答辩时拿到录用通知,投期刊等5月底拿录用通知有点悬。

-

本文章使用limfx的vscode插件快速发布