F29-CZ11-7030板卡作为子卡进行数据采集并发送(20251112)

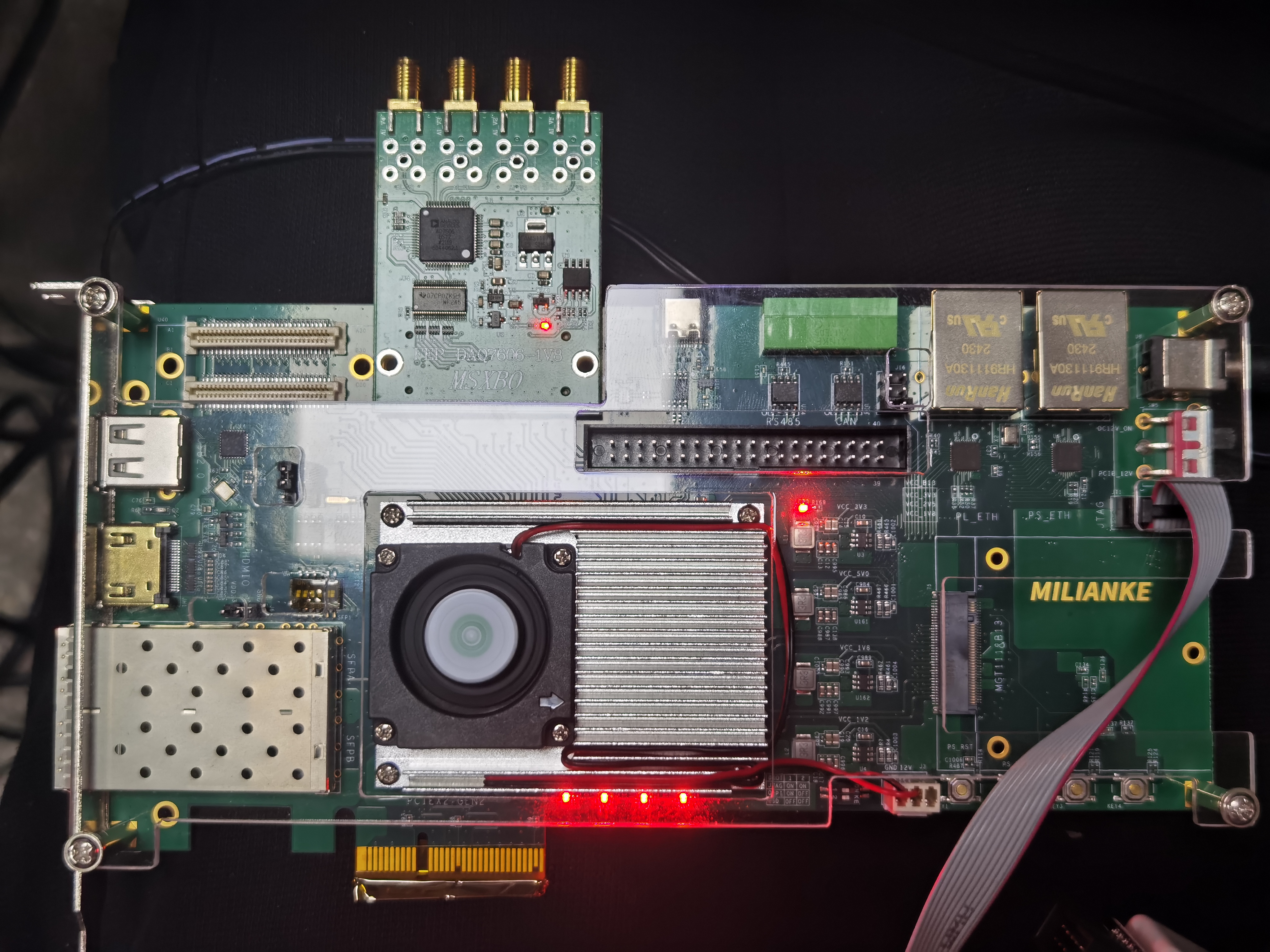

通过ad7606板卡进行采集

程序代码方面,和之前的没有什么区别,直接将旧代码拿来用,根据硬件手册说明调整约束文件后就可以。

需要使用1.8V的ad7606板卡。

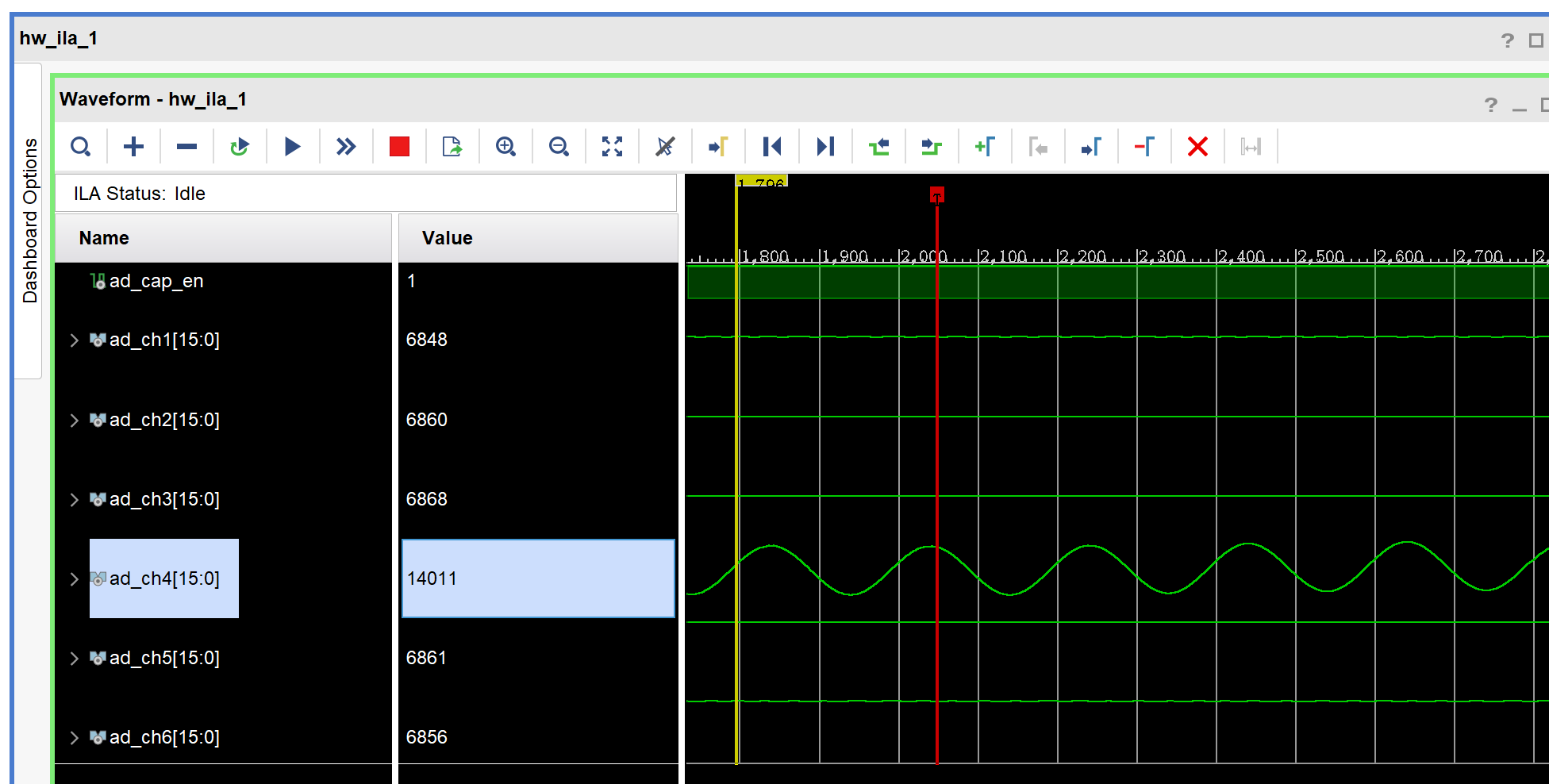

这个ad7606板卡,各个通道与程序中的变量关联是,从右向左,分别为程序中的ch1到ch4。

使用1KHz的正弦波输入,在程序中,设定的采样率为200K,因此采样周期为5us,此时200个采样周期等同于正弦波信号的一个周期。查看测试抓取的信号可知,测试结果符合预期。

将采集数据从子卡发送至主卡

整体逻辑并不复杂,就是将采集的数据与之前做的数据传输内容连接,让采集的内容可以在子卡端经过协议编码后发送至主卡。

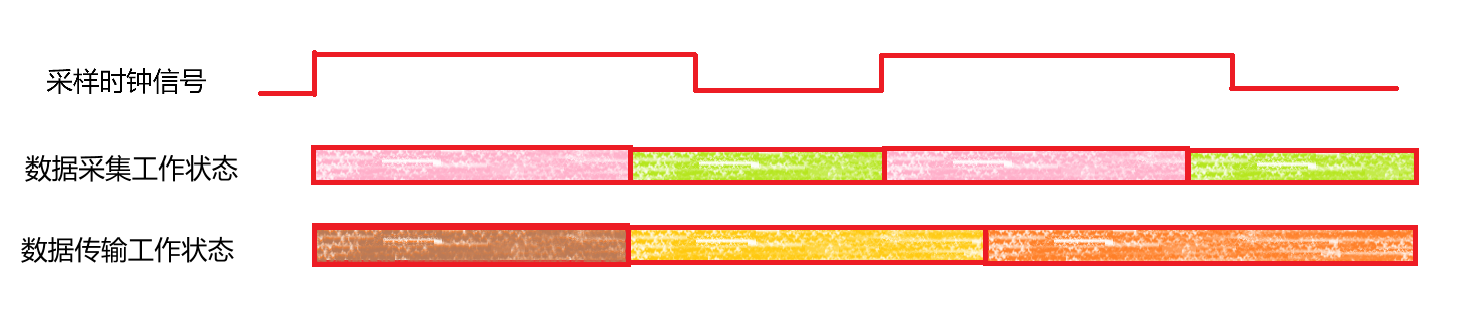

原来的逻辑里面,数据传输部分工作状态受采样时钟信号控制。即,每次接收到采样时钟信号上升沿后跳出idle状态,进入ready状态,等待数据到来,之后接收到数据就跳转working状态,开始进行传输,直到单次采样数据全部传输后回到idle状态,并等待新的数据到来。

现在采样时钟信号上升沿到来后,采集卡进行采样,采样本身会花费时间,因此数据传输部分需要等待采样完成后,才能接收到信号并进行数据传输。在原来的设计下,此时需要保证,数据采集工作与数据传输工作在一个采样周期内完成,否则会出现下图的问题:

图中采样时钟信号第一个上升沿到来,数据采集模块开始进行采集,用粉色表示,同时数据传输模块进入准备状态,等待采集数据到来,用褐色表示;完成采集后,采集模块跳转至idle状态等待下一采样周期到来,用绿色表示,同时数据传输模块接收到采样数据,开始进行编码工作并通过高速收发器发送数据,用黄色表示;完成本次采样的所有采集数据发送后,跳回idle状态,用橙色表示。

如图,如果数据传输模块工作时间过久,在下一采样周期到来之前还没有完成数据采集,那么在下一个采样周期中,数据传输模块停留在idle状态,无法跳转至ready状态,因而会导致该周期的采样数据无法接收并传输,实际表现就是采样频率低于设定值。如果数据采集工作与数据传输工作所需时间均分别短于一个采样周期,但两者加起来长于一个采样周期,那么上述旧设计,实际就是导致了系统采样率性能的限制。

有两种解决方法。

- 第一种是,数据传输模块不再受采样时钟信号控制,每次完成数据传输工作后跳至idle状态,idle状态持续一段时间后自动跳到ready状态,等待新一轮的采集数据;

- 第二种是,修改状态逻辑,不再设置ready状态,数据采集模块完成采集会输出使能信号,提示当前的采集数据已经更新;此时数据传输模块直接根据数据采集模块输出的使能信号跳转至working状态。

上述两种方案本质上都是将数据传输模块工作的控制从采样时钟信号调整为数据采集模块相关信号。

由于当前使用的ad7606采集卡最高采样率仅为200K,采样周期较长,并未出现上述的无法一个周期内完成数据采集与传输两部分工作的问题,目前旧的控制逻辑下,相关程序已经实现仿真测试,数据编码模块可以实现编码数据的输出,正在修改新的状态控制逻辑。另外,xczu7eg主卡上已经有相关的数据接收模块程序,后续还需要修改相关状态控制逻辑,并测试能否将CZ11-7030板卡数据发送至主卡上。

PL端将采集数据通过UDP发送至上位机

杰哥帮着修改了之前PL端的程序,将原来数据源,从模拟生成的假数据换成了ad7606板卡的真数据。后面还需要测试程序是否可以正确采集数据,并检测最终发送到上位机的UDP包内数据是否符合预期。

本文章使用limfx的vscode插件快速发布