示波器测量ddaq PL端程序相关时延(20251208)

示波器读取数据

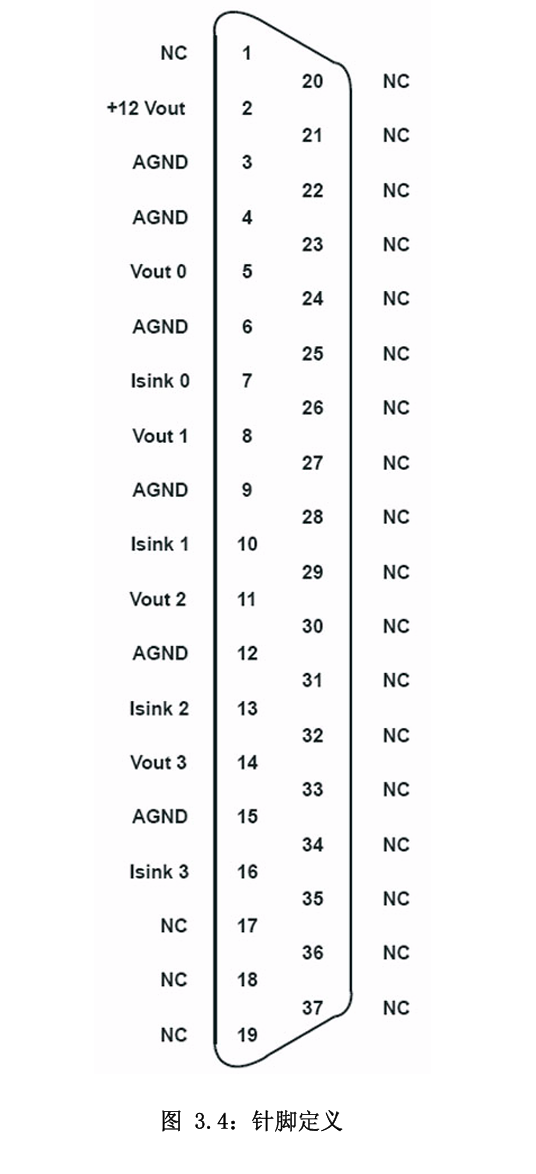

PCI-1720U板卡DB37针脚定义如下:

各个信号描述如下:

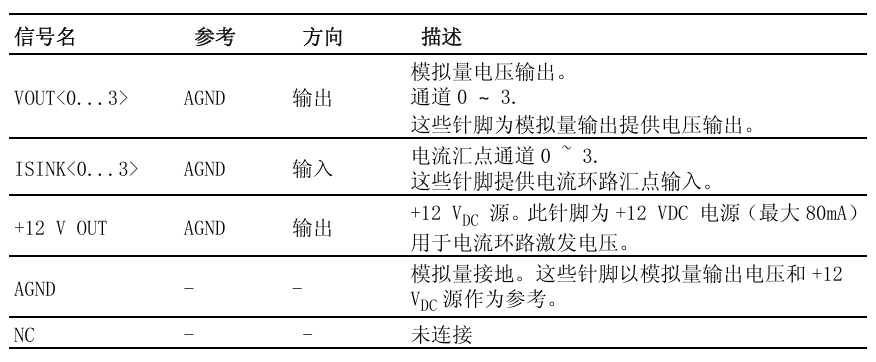

要让示波器读取到某一通道的数据,就需要让示波器接收信号的探针连接到对应通道信号输入输出通路上,其中,PCI-1720U输出的信号,从对应通道的Vout输出,然后通过对应Isink流回。

例如,要读取通道0的数据,就需要将Vout0和Isink0相连接,示波器探针与该通路相连。如下图所示:

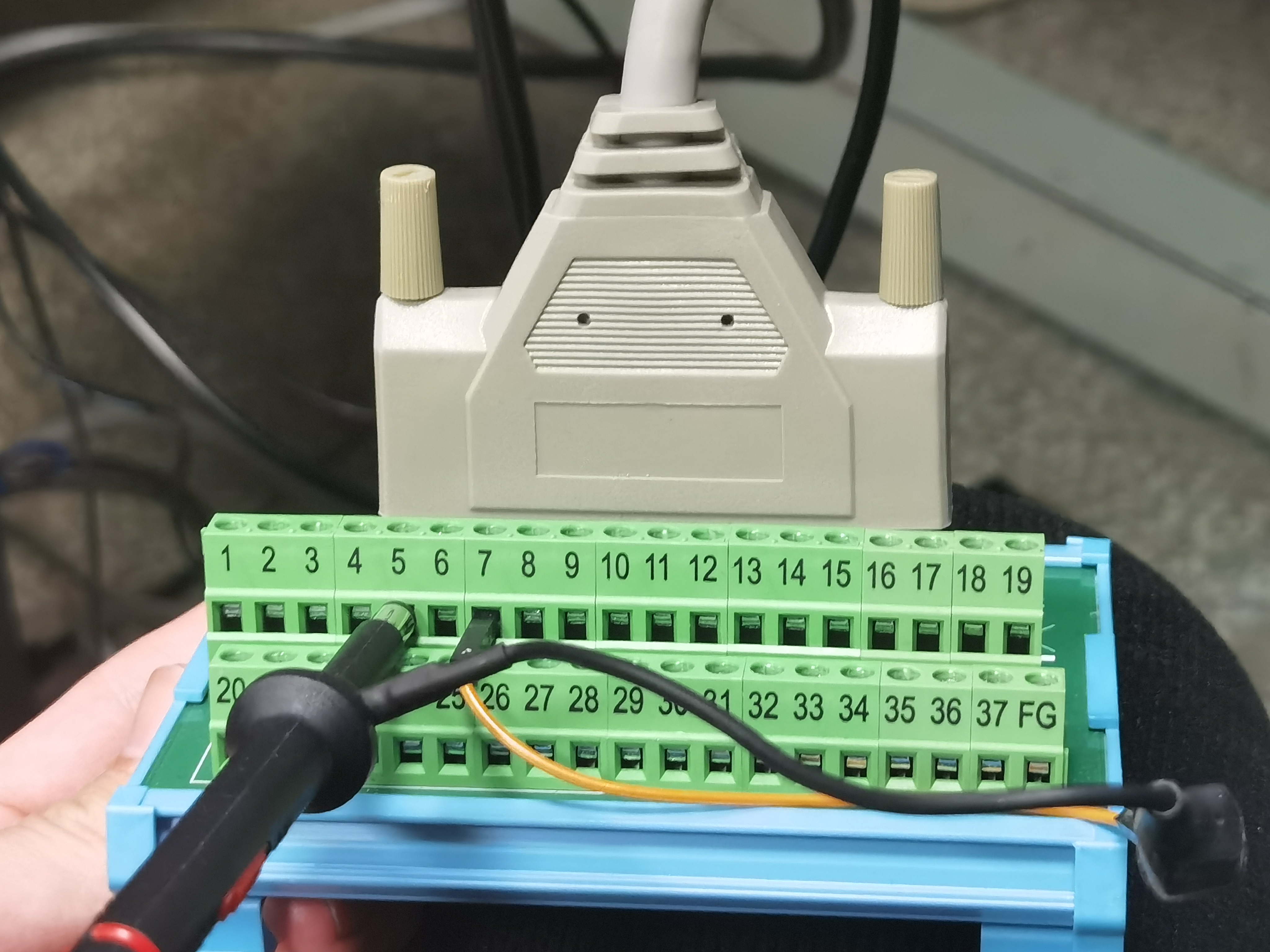

当通道1输出2khz方波信号时,在示波器上测量得到:

测量得到信号频率为2khz,与信号源频率一致。

测量得到信号频率为2khz,与信号源频率一致。

可见,可以通过该连线方式使示波器读取到PCI-1720U的输出信号。

系统延时测量思路

测量系统延时,可以选择两个时间点,测量两个时间点之间的时差。其中一个时间点是开始采集后,FPGA完成一次采样的时刻,另一个时间点是,上位机接收到一个数据包的时刻。

具体实施上,可以通过FPGA和电脑的PCI-1720U分别输出信号,由示波器测量实现。FPGA上选择一个引脚,该引脚用于输出脉冲信号,脉冲信号在FPGA完成一次采样时产生;PCI-1720U板卡由DB37接口,在上位机编写一个测试程序,当上位机接收到一个数据包后,所选择的通道产生一次脉冲信号。两个信号均通过同一个示波器接收到不同通道并显示。

已经完成上位机测试程序编写,可以在示波器上检测到相关信号变化,还需要等到适合的io拓展卡拿到手后,再抓取FPGA的相关信号。

示波器显示屏上方显示了两个通道的信号波形,其中通道1,黄色信号为上位机输出的信号,该信号在上位机接收到UDP包后会改变当前电平。通道2准备设计为FPGA输出的信号,该信号在完成一次采样点的采样后会发生变化。后续发现示波器抓取信号的触发条件只能设置为通道1,因此将两信号所用通道交换。

操作流程如下:

- 首先将通道1的探针与FPGA的对应引脚连接,通道2与PCI-1720U对应通道相连接。(目前程序使用FEP端口输出数据,FEP转接卡上是选择CEP1的针脚3,可以用杜邦线母口与之相连。)

- 上位机的/home/ddaq/udpdk/apps/dd/example路径下,有udp_ao程序可以在接收到FPGA发送的第一个UDP包时产生高电平信号,输入ctrl+C退出该程序;在交换机开机后,进入root,跳转到对应文件夹,输入

./udp_ao执行程序。 - 按下“单次”后可以根据触发条件抓取相关信号,找到"单次"按键下的“菜单”按键,点击后可以调整触发条件等,此时根据通道1输出的脉冲信号电平情况,按下“电平”按键,设置合适的触发预置电平(可设置为1.5V)。

- 之后按FPGA板上的按键3,即可执行采样,相关信号波形与电平变化将会在示波器上显示。

- 测量系统具体时延时。按下“光标”,可以看到波形图里面有用于测量时间的两个光标,可以通过旋转旋钮改变光标位置,此时界面会显示对应光标相对触发时刻的时间差;将两个光标分别放在两个信号的起始位置,分析时间差,即可测量得出系统采集与传输的延时;此时还可以通过旋转“标度”旋钮,提升光标测时间差的精度。

测量结果

根据上述操作,抓到波形,将光标a移动到通道1中第一个脉冲信号的位置:

然后转动旋钮,将观察范围移动到通道2上升起始的位置,从而便于精确移动光标b:

显示两个光标时间差为325.40us,即本次采样,采集到第一个数据到上位机接收到第一个UDP包的时延为325.40us。

后续重复了几次测量,平均时延大约为0.3ms。

后续分析

观察可以看到,通道2,也就是上位机输出的信号,所产生的方波信号上升沿时间长达5us,相当于ad7606采集周期时长了,相较于FPGA输出的脉冲信号,精度有极大差距。

另一方面,此方案只适合测量第一次采集数据到第一个UDP包接收的时延。虽然程序中设置,接收到UDP包后PCI卡输出5us的高电平就拉低,但是实际高电平时间长达800us以上,远长于设定时间,如果在高电平期间再来新的UDP包,就无法检测到相关信号变化,因此后续UDP包的相关时延难以测量。

正在调研ptp协议。

本文章使用limfx的vscode插件快速发布