directDAQ第二次测延时

第二次测延时的方法

fpga端取的时间点为即将发送的每个包的上升沿,具体来说,是仿真图中的sfp_signal

上位机端取的时间点为dpdk程序每收到一个包时立马输出的上升沿

并且对上位机程序进行了专门的优化,减少了无关的输出,这次测试用的上位机程序路径为

/home/ddaq/udpdk/apps/dd/dpdk_short

执行命令为(root模式下)

./dpdk_short -c config.ini

第二次测延时的结果

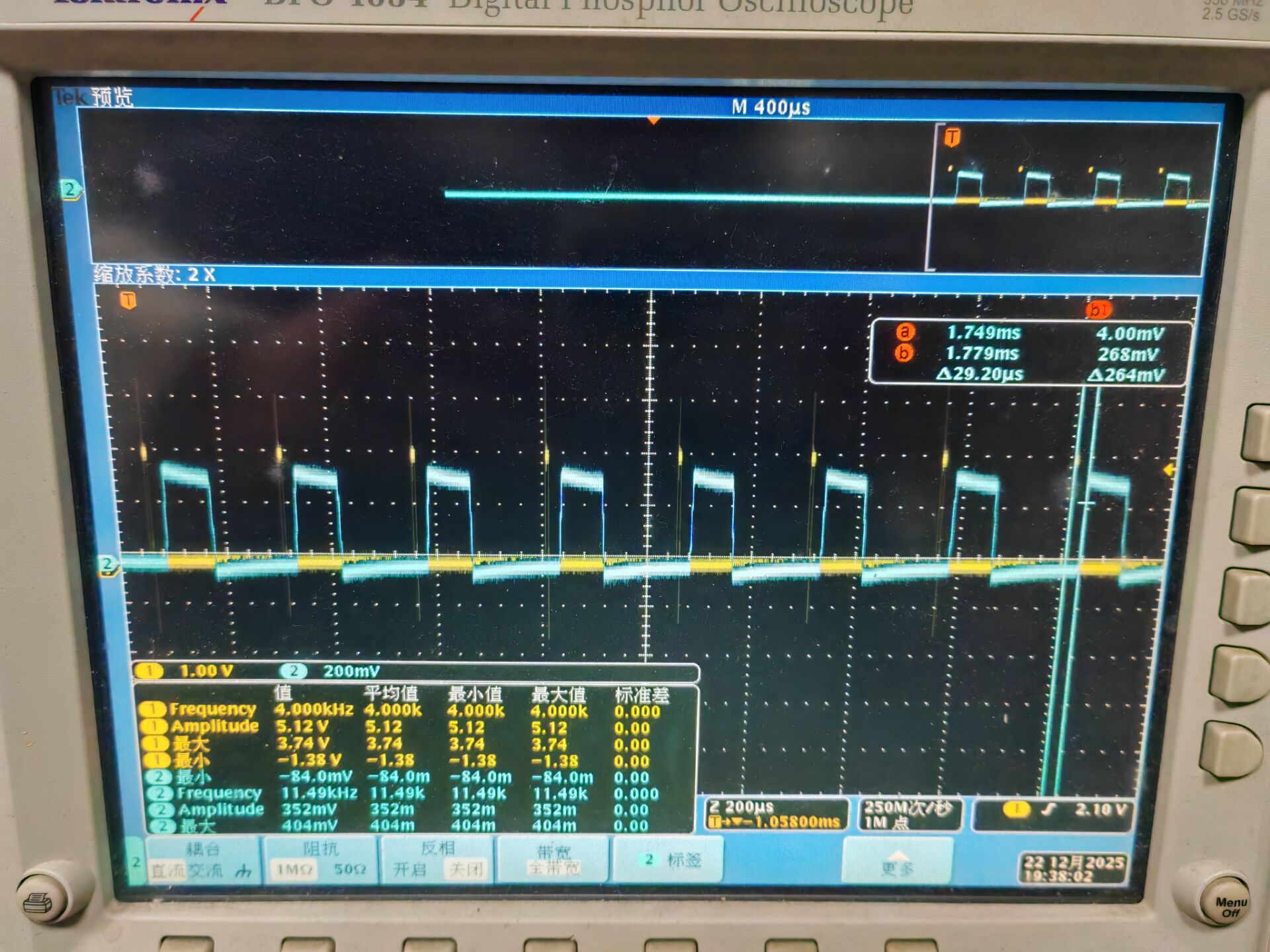

设置采集500个点,sample_coef设置为10,则会传输50个点,一共传输10个udp包,预计会有10个脉冲

结果如图所示

可以看到有多个黄色和蓝色脉冲,黄色脉冲代表fpga输出的上升沿脉冲,蓝色脉冲代表上位机输出的上升沿脉冲

其中,每个黄色上升沿和蓝色上升沿的时延基本都为30us左右

本文章使用limfx的vscode插件快速发布