ad子卡程序分析

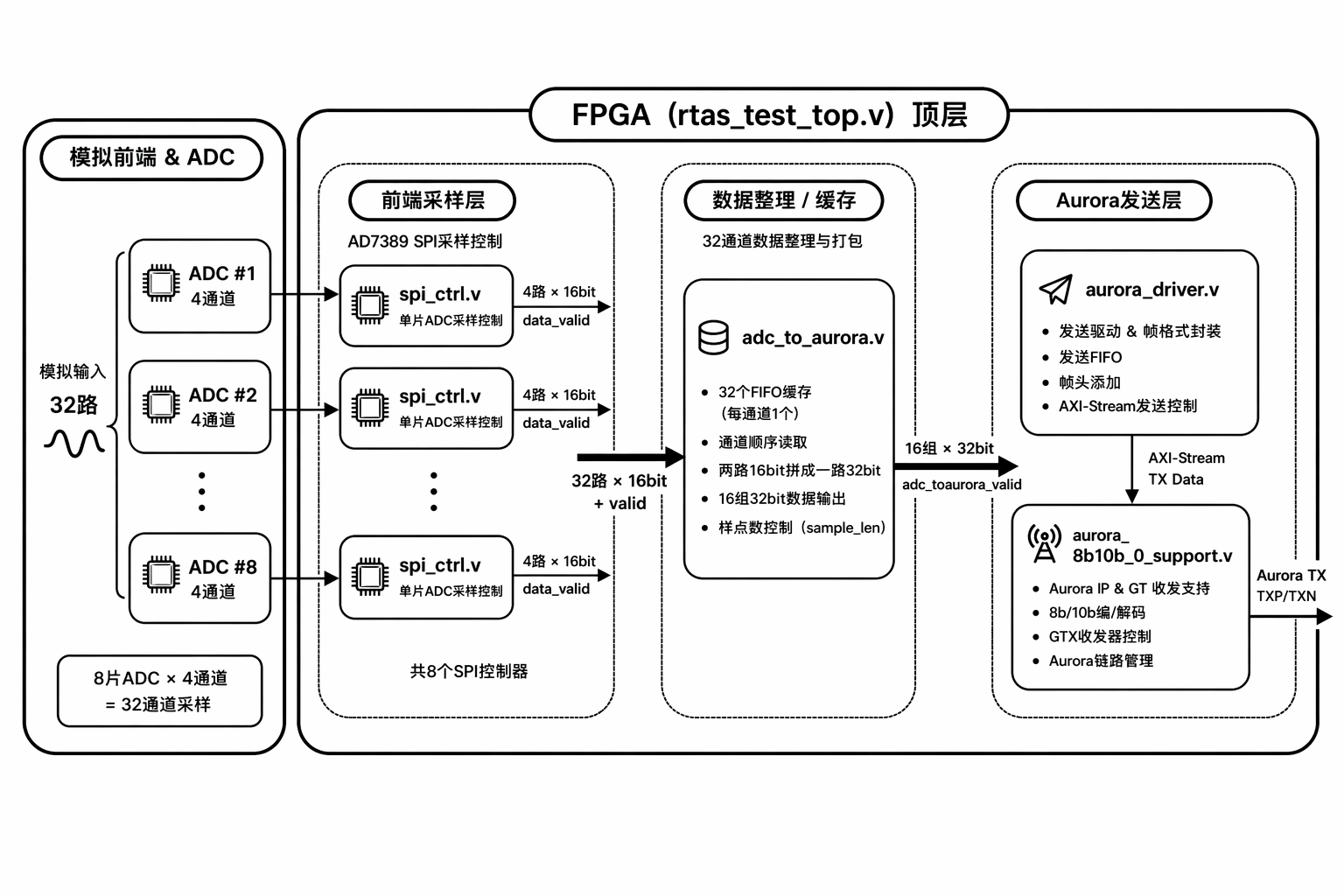

工程框架

顶层输入输出

因为当前的目的是知道如何使用这块ad子卡,所以这里主要展示了与主卡对接的输入输出。

module rtas_test_top(

input sys_clk, //子卡的系统时钟输入

input start_stop, //该信号高电平,子卡开始工作,拉低后子卡停止工作

input fmc_reset, //外部复位信号

// Clocks

input GT_REFCLK_P,

input GT_REFCLK_N,

// GT Serial I/O

input RXP,

input RXN,

output TXP,

output TXN

);

关键参数配置

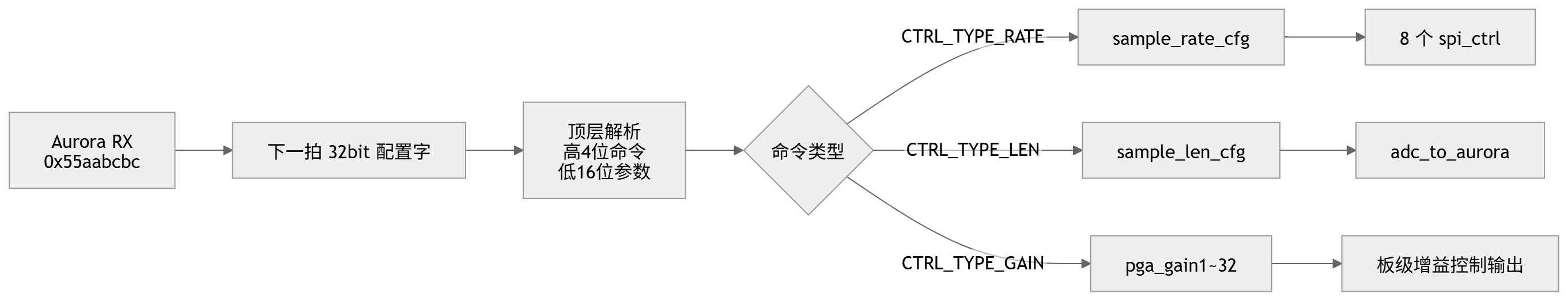

参数主要是由主卡通过aurora传到子卡,然后子卡进行配置。

每次传输的数据帧结构:

rx_tdata_i = 0x55aabcbc // 数据帧头,表明后面的数据是参数配置

rx_tdata_i = {ctrl_cmd_reg[31:28], useless_ctrl_byte[27:16], ctrl_cmd_data[15:0]}

······

-

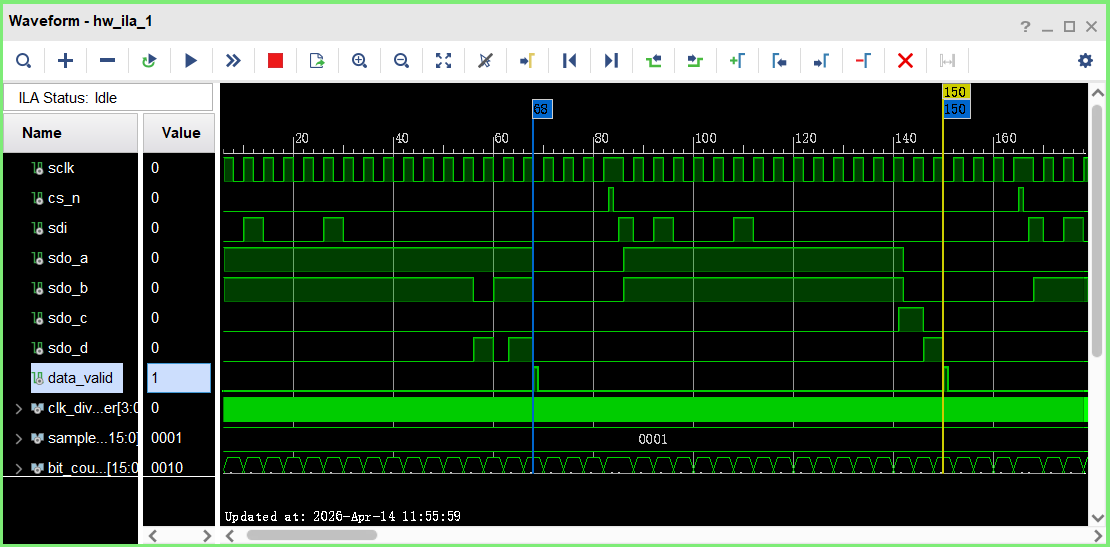

采样率设置 子卡中虽有sample_rate这个参数,但这个参数实际上是表征每次adc转换的时候等待的周期数

if (sample_cnt >= (sample_rate_eff - 1'b1)) begin sample_cnt <= 16'd0; conv_busy <= 1'b1; conv_start <= 1'b1; sclk_enable <= 1'b1; end经过推算得出实际采样率为:

adc_clk/(81+sample_rate)。这里adc_clk一般为160MHz,sample_rate最小为1。但这样的话,最大采样率只是接近2M,但无法严格等于2M。从图中ILA可以看出,实际每次data_valid之间间隔82个adc_clk采样周期。 因此我对spi_ctrl进行修改,将实际采样率变为:

因此我对spi_ctrl进行修改,将实际采样率变为:adc_clk/(77+sample_rate)。这样adc_clk为160MHz时,只需使sample_rate为3,即可实现2M的实际采样率。 -

采样长度设置 子卡中sample_len实际作用于adc_to_aurora模块,采样点数满足sample_len时,adc_to_aurora模块就不会往下一个传输数据,然后再次开始采集前,所有存储数据的fifo会进行清零操作。 如果采样点数设置为0,就默认是连续采集。

本文章使用limfx的vscode插件快速发布