开坑:Verilog HDL学习 【1】

萌新小白,为做FPGA大创,开始学习Verilog HDL

Verilog是什么

HDL原名Hardware Description Language(硬件描述语言),用来描述电路的功能和数据的流向,然后由逻辑综合工具自动综合出由逻辑门及其相互连接构成的电路结构细节,实现HDL描述的功能。

Verilog HDL的优点

1、语法简单,类似于C语言

2、可以从不同层次进行描述:开关、门、RTL、行为等各个层次

3、比较流行

4、编程语言接口是Verilog语言特性之一,设计者可以通过编写的C代码访问Verilog内部数据结构

设计方法:从上而下,即从目的出发,把功能拆解成小的模块;自下而上,从模块出发,组成大的功能模块。模块间不能嵌套饮用。

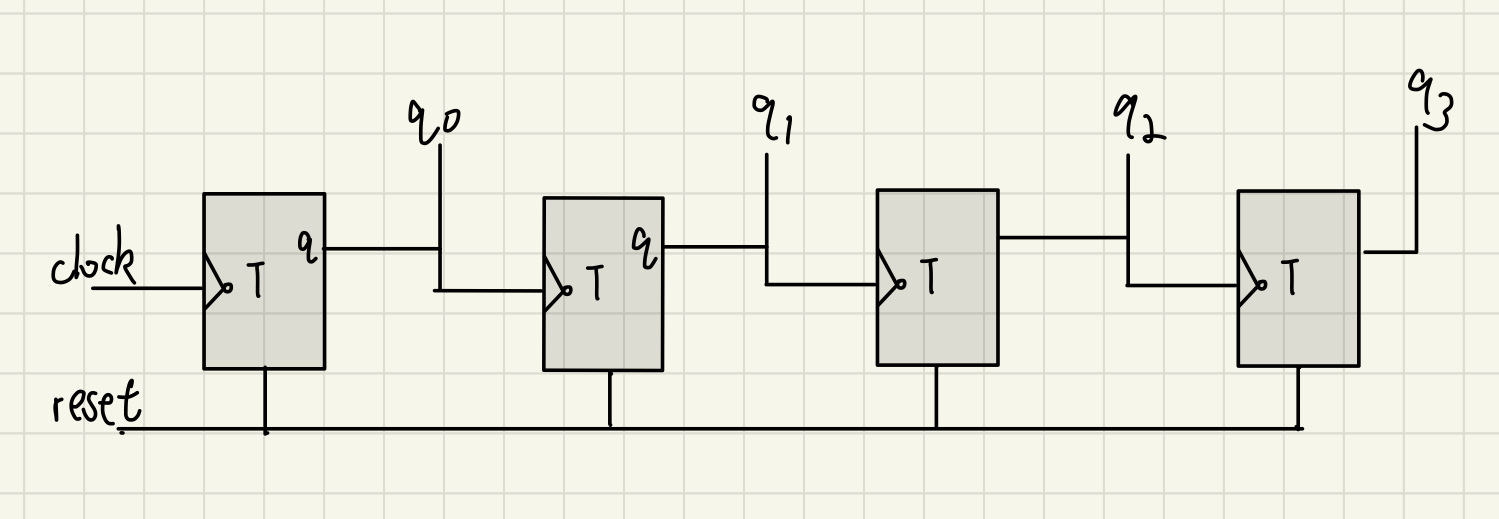

一个4位脉冲进位计数器

module ripple_carry_counter(q,clk,reset);

output [3:0] q;

input clk,reset;

T_FF tff0(q[0],clk,reset);

T_FF tff1(q[0],clk,reset);

T_FF tff2(q[0],clk,reset);

T_FF tff3(q[0],clk,reset);

endmodule//顶层模块,模块引用有点像C++里的类

module T_FF(q,clk,reset);

output q;

input clk,reset;

wire d;

D_FF dff0(q,d,clk,reset);

not n1(d,q);

endmodule//T触发器

module D_FF(q,d,clk,reset);

output q;

input d,clk,reset;

reg q;

always @(posedge reset or negedge clk)

if(reset)

q<=1'b0;

else q<=d;

endmodule//D触发器逻辑仿真的两种方式:在激励块中调用并直接驱动;在虚拟顶层模块中调用激励块和设计块。以下是激励块

module stimulus;

reg clk;

reg reset;

wire [3:0] q;

ripple_carry_counter r1(q,clk,reset);

initial

clk=1'b0;

always

#5 clk=~clk;

initial

begin

reset=1'b1;

#15 reset 1'b0;

#180 reset 1'b0;

#10 reset 1'b0;

#20 $finish;

end

initial

$monitor($time,"Output q=%d",q);

endmodule