开坑:Verilog HDL学习 【6】

萌新小白,为做FPGA大创,开始学习Verilog HDL

时序和延迟

延迟类型

分布延迟:每次过门的延迟

and #5 a1(3,a,b)

集总延迟:模块输入到输出的延迟。设定延迟时只在输出门设置最大延迟

引脚到引脚延迟:路径延迟

路径延迟建模

specify

specify (a=>out[0])=9; (b=>out[1])=9; endspecify//specify是一个独立的部分,并行连接 specify (a,b*>out)=9; c,d*>out)=11;//全连接(对应到每个输出口) endspecify (posedge clock=>(out+:in))=(10:8);//边沿敏感

specparam语句

类似于参数设定,但是仅用在specify内部

specparam t_01=8:9:10;

时序检查

$setup,$hold,$width $setup(data_event,reference_event,limit); $hold(reference_event,data_event,limit); $width(reference_event,limit);

开关级建模

用的比较少,可以自己构建元件,要求对电路知识比较熟悉。

nmos、pmos、cmos、双向开关、电源和地、阻抗开关

nmos n1(out,data,control1); pmos n2(out,data,control2); cmos n3(out,data,nontrol,pcontrol); tran t1(inout1,inout2); tranif0(1) t(inout1,inout2,control); supply1 vcc; supply0 gnd; rnmos\rpmos\rcmos\rtran\rtranif0\rtranif1;

或非门

module my_nor(out,a,b);

output out;

input a,b;

supply1 pwr;

supply0 gnd;

pmos(c,pwr,b);

pmos(out,c,a);

nmos(out,gnd,a);

nmos(out,gnd,b);

endmodule用户自定义原语(UDP)

定义自己的原语(原语:例如and、nand、or等)

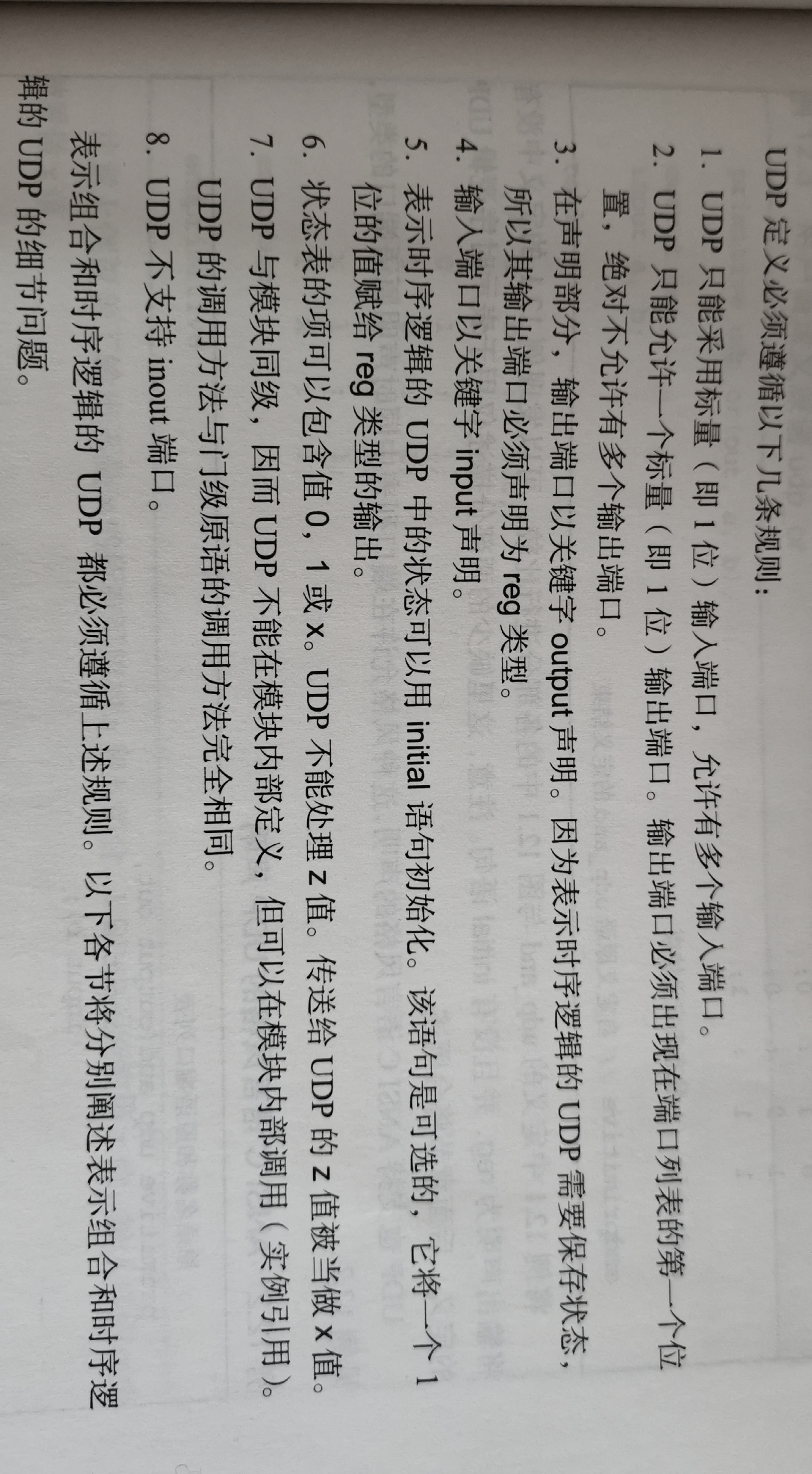

一些设计要求

primitive udp_or(out,a,b);

output out;

input a,b;

table

//

a b : out;

0 0 : 0;

1 ? : 1;

? 1 : 1;

x 0 : x;

0 x : x;//列写真值表,无关项用?

endtable

endprimitive下面介绍一个时序的例子

primitive edge_dff(output reg q=0,input d,clock,clear);

table

// d clock clear :q:q+;

? ? 1:?:0;

? ? f:?:-;

1 f 0:?:1;

0 f 0:?:0;

? (1x) 0:?:-;

? p 0:?:-;

* ? 0:?:-;

endtable

endprimitive//式子中的f、p、*等代表电位变化,可查表书目参考:Verilog HDL数字设计与综合(第二版)[美] Samir Palnitkar