ILA集成逻辑分析器

https://www.xilinx.com/products/intellectual-property/ila.html#overview

AnswerRecord:https://www.xilinx.com/support/answers/54606.html

ILA可以用来监听设计的内部信号。

FPGA设计中的信号都接入到clk和probe输入引脚

这些接入probe的信号,都以design speed(设计速度?)采样并且存储在BRAM里面。

来总结一下上面的理解:

probe接口接入需要监控的信号,然后每个probe接口处都有一个Probe Trigger Comparator,然后所有的Probe Trigger Comparator的条件and或者or构成出发整个ILA的事件。设置这个触发事件需要通过Vivado logic analyzer这个软件。当这个出发事件发生,就可以看到波形了。

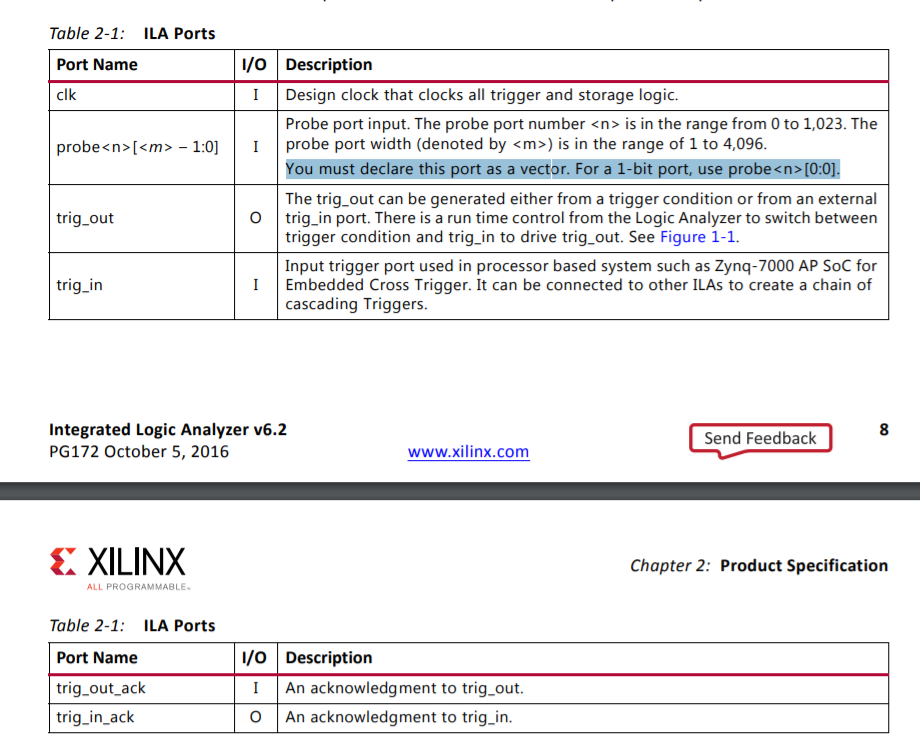

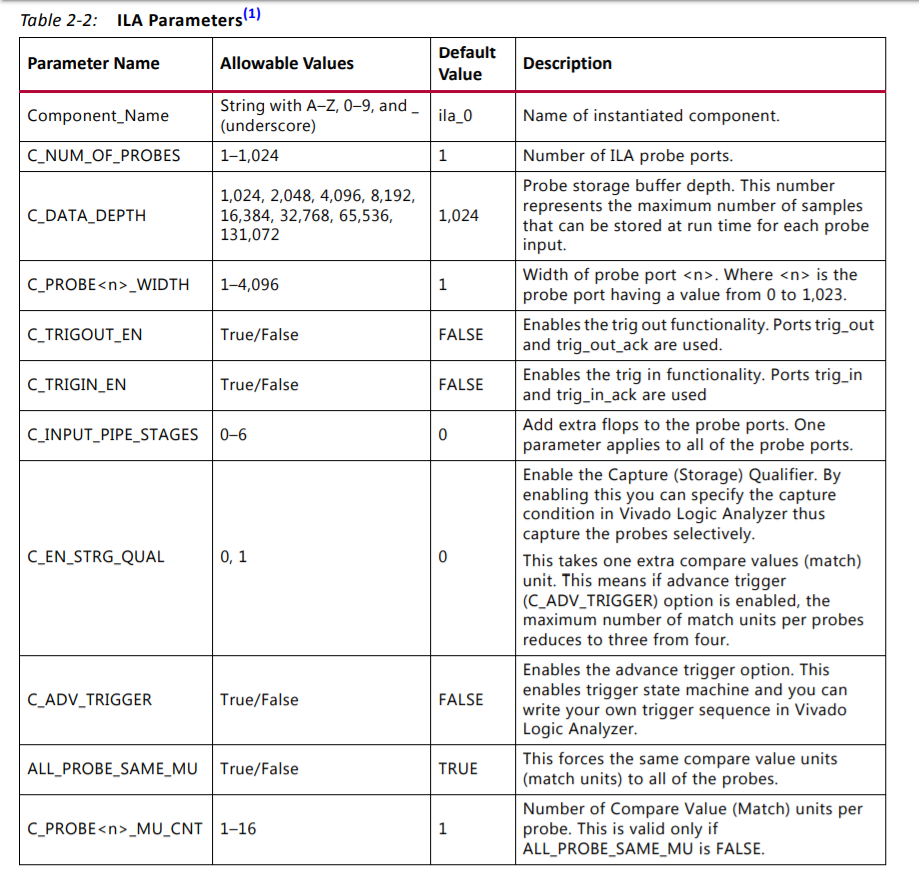

最多1024个probe,每个probe的数据宽度最多为4096. probe连接到需要监控的信号

clk:时钟频率,也是信号的采样频率,应该和设计的时钟频率保持一致,才能正确采集信号的数据

本文章使用limfx的vsocde插件快速发布